# Intel<sup>®</sup> Core<sup>™</sup> i7 Processor Families for the LGA2011-0 Socket

Thermal Mechanical Specification and Design Guide

- Supporting Desktop Intel<sup>®</sup> Core<sup>™</sup> i7-3970X and i7-3960X Extreme Edition Processor Series for the LGA2011-0 Socket

- Supporting Intel<sup>®</sup> Core<sup>™</sup> i7-3000K Processor Series and Intel<sup>®</sup> Core<sup>™</sup> i7-3000 Processor Series for the LGA2011-0 Socket

- Supporting Desktop Intel<sup>®</sup> Core<sup>™</sup> i7-4960X Extreme Edition Processor Series for the LGA2011 Socket

- Supporting Desktop Intel<sup>®</sup> Core<sup>™</sup> i7-49xx and i7-48xx Processor Series for the LGA2011 Socket

November 2013

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The processors and LGA2011-0 socket may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The code names presented in this document are only for use by Intel to identify products, technologies, or services in development, that have not been made commercially available to the public, i.e., announced, launched or shipped. They are not "commercial" names for products or services and are not intended to function as trademarks.

Requires a system with Intel® Turbo Boost Technology capability. Consult your PC manufacturer. Performance varies depending on hardware, software and system configuration. For more information, visit http://www.intel.com/technology/turboboost

Intel, Intel Core, and the Intel logo are trademarks of Intel Corporation in the U.S and other countries.

\* Other brands and names may be claimed as the property of others.

Copyright © 2013, Intel Corporation.

# Contents

| 1 | Intro                                                                                                      | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

|---|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|   | 1.1                                                                                                        | Definition of Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

|   | 1.2                                                                                                        | Related Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                                                                                                             |

| 2 | Pack                                                                                                       | age Mechanical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13                                                                                                             |

|   | 2.1                                                                                                        | Package Mechanical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                                                             |

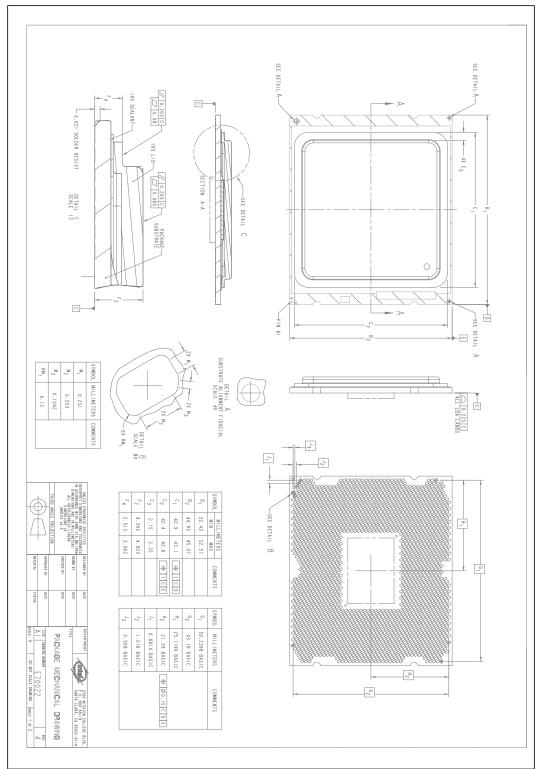

|   |                                                                                                            | 2.1.1 Package Mechanical Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

|   |                                                                                                            | 2.1.2 Processor Component Keepout Zones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

|   |                                                                                                            | 2.1.3 Package Loading Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

|   |                                                                                                            | 2.1.4 Package Handling Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

|   |                                                                                                            | 2.1.5 Package Insertion Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

|   |                                                                                                            | 2.1.6 Processor Mass Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|   |                                                                                                            | 2.1.7 Processor Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

|   |                                                                                                            | 2.1.8 Processor Markings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

| 3 | LGA2                                                                                                       | 2011-0 Socket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

|   | 3.1                                                                                                        | Contact / Land Mating Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|   | 3.2                                                                                                        | Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|   | 3.3                                                                                                        | Attachment to Motherboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

|   | 3.4                                                                                                        | Socket Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

|   |                                                                                                            | 3.4.1 Socket Body Housing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

|   |                                                                                                            | 3.4.2         Solder Balls           3.4.3         Contacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |

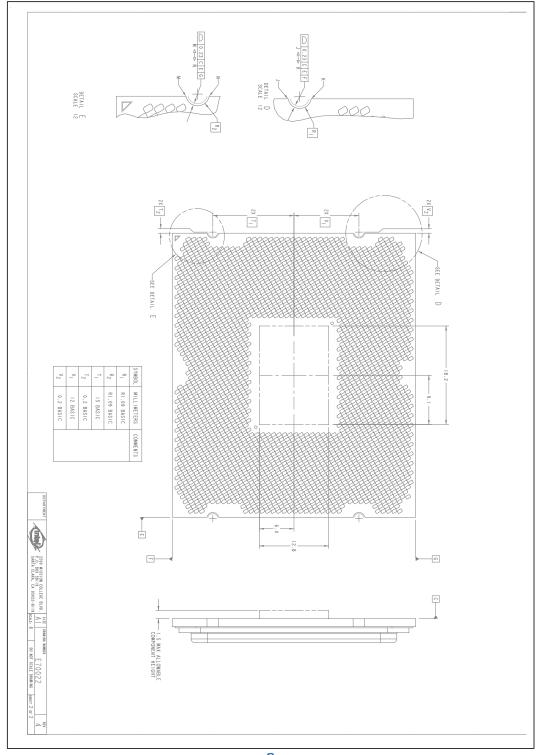

|   |                                                                                                            | 3.4.4 Pick and Place Cover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

|   |                                                                                                            | 3.4.5 Socket Standoffs and Package Seating Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

|   | 3.5                                                                                                        | Durability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

|   | 3.6                                                                                                        | Markings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

|   | 3.7                                                                                                        | Component Insertion Forces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

|   | 3.8                                                                                                        | Socket Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |

|   |                                                                                                            | 506ket 5/2e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                                                                             |

| 4 |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |

| 4 | Inde                                                                                                       | pendent Loading Mechanism (ILM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                                             |

| 4 |                                                                                                            | pendent Loading Mechanism (ILM)<br>Square ILM Design Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26<br>27                                                                                                       |

| 4 | Inde                                                                                                       | pendent Loading Mechanism (ILM)Square ILM Design Concept4.1.1Square ILM Assembly Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26<br>27<br>27                                                                                                 |

| 4 | Inde<br>4.1                                                                                                | pendent Loading Mechanism (ILM)<br>Square ILM Design Concept<br>4.1.1 Square ILM Assembly Design Overview<br>ILM Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26<br>27<br>27<br>29                                                                                           |

| 4 | Inde<br>4.1                                                                                                | pendent Loading Mechanism (ILM)<br>Square ILM Design Concept<br>4.1.1 Square ILM Assembly Design Overview<br>ILM Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26<br>27<br>27<br>29<br>29                                                                                     |

| 4 | Inde<br>4.1                                                                                                | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1       Square ILM Assembly Design Overview         ILM Features         4.2.1       ILM Closing sequence         4.2.2       ILM Opening Sequence         4.2.1.1       ILM Keying                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26<br>27<br>27<br>29<br>29<br>30<br>31                                                                         |

| 4 | Inde<br>4.1<br>4.2                                                                                         | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1       Square ILM Assembly Design Overview         ILM Features         4.2.1       ILM Closing sequence.         4.2.2       ILM Opening Sequence.         4.2.3       ILM Keying.         4.2.3       ILM Back Plate Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                     | 26<br>27<br>27<br>29<br>29<br>30<br>31<br>31                                                                   |

| 4 | Inde<br>4.1                                                                                                | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1       Square ILM Assembly Design Overview         ILM Features         4.2.1       ILM Closing sequence.         4.2.2       ILM Opening Sequence.         4.2.3       ILM Keying.         4.2.3       ILM Back Plate Design Overview         ILM Assembly                                                                                                                                                                                                                                                                                                                                                                                                | 26<br>27<br>29<br>29<br>30<br>31<br>31<br>32                                                                   |

| 4 | Inde<br>4.1<br>4.2<br>4.3                                                                                  | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow                                                                                                                                                                                                                                                                                                                                                                                                              | 26<br>27<br>29<br>30<br>31<br>31<br>32<br>32                                                                   |

| 4 | Inde<br>4.1<br>4.2<br>4.3<br>4.4                                                                           | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation                                                                                                                                                                                                                                                                                                                                                                               | 26<br>27<br>29<br>30<br>31<br>31<br>32<br>32<br>33                                                             |

| 4 | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                                    | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation         ILM Cover                                                                                                                                                                                                                                                                                                                                                             | 26<br>27<br>29<br>29<br>30<br>31<br>31<br>32<br>32<br>33<br>34                                                 |

| 4 | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                             | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence         4.2.2 ILM Opening Sequence         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation         ILM Cover         Heatsink to ILM interface                                                                                                                                                                                                                                                                                                                             | 26<br>27<br>29<br>29<br>30<br>31<br>31<br>32<br>32<br>33<br>34                                                 |

| 5 | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2                                                     | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence         4.2.2 ILM Opening Sequence         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation         ILM Cover         Heatsink to ILM interface         2011-0 Socket and ILM Electrical, Mechanical, and                                                                                                                                                                                                                                                                   | 26<br>27<br>29<br>30<br>31<br>32<br>32<br>33<br>34<br>36                                                       |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir                                            | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence         4.2.2 ILM Opening Sequence         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation         ILM Cover         Heatsink to ILM interface         2011-0 Socket and ILM Electrical, Mechanical, and ronmental Specifications                                                                                                                                                                                                                                          | 26<br>27<br>29<br>29<br>30<br>31<br>31<br>32<br>32<br>33<br>34<br>36<br>37                                     |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1                                     | pendent Loading Mechanism (ILM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26<br>27<br>29<br>29<br>30<br>31<br>31<br>32<br>32<br>33<br>34<br>36<br>37<br>37                               |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1<br>5.2                              | <pre>pendent Loading Mechanism (ILM)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26<br>27<br>29<br>30<br>31<br>32<br>32<br>33<br>34<br>36<br>37<br>37<br>37                                     |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1<br>5.2<br>5.3                       | pendent Loading Mechanism (ILM). Square ILM Design Concept 4.1.1 Square ILM Assembly Design Overview ILM Features 4.2.1 ILM Closing sequence. 4.2.2 ILM Opening Sequence. 4.2.2.1 ILM Keying. 4.2.3 ILM Back Plate Design Overview ILM Assembly 4.3.1 Manufacturing Assembly Flow Processor Installation ILM Cover Heatsink to ILM interface. 2011-0 Socket and ILM Electrical, Mechanical, and component Mass. Package / Socket Stackup Height Loading Specifications.                                                                                                                                                                                                                                                                   | 26<br>27<br>29<br>30<br>31<br>32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37                               |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1<br>5.2<br>5.3<br>5.4                | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.2.1 ILM Keying.         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation.         ILM Cover         Heatsink to ILM interface.         2011-0 Socket and ILM Electrical, Mechanical, and         ronmental Specifications.         Component Mass.         Package / Socket Stackup Height         Loading Specifications.         Electrical Requirements.                                                                | 26<br>27<br>29<br>30<br>31<br>32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>38                         |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5         | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.2.1 ILM Keying.         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation.         ILM Cover         Heatsink to ILM interface.         2011-0 Socket and ILM Electrical, Mechanical, and         ronmental Specifications.         Component Mass.         Package / Socket Stackup Height         Loading Specifications.         Electrical Requirements.         Environmental Requirements                             | 26<br>27<br>29<br>29<br>30<br>31<br>31<br>32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>37<br>38<br>39 |

|   | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Ther | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.2.1 ILM Keying         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation         ILM Cover         Heatsink to ILM interface         2011-0 Socket and ILM Electrical, Mechanical, and         ronmental Specifications         Component Mass         Package / Socket Stackup Height         Loading Specifications         Electrical Requirements         Environmental Requirements         Environmental Requirements | 26<br>27<br>29<br>30<br>31<br>32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>38<br>39<br>40             |

| 5 | Inde<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>LGA2<br>Envir<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5         | pendent Loading Mechanism (ILM)         Square ILM Design Concept         4.1.1 Square ILM Assembly Design Overview         ILM Features         4.2.1 ILM Closing sequence.         4.2.2 ILM Opening Sequence.         4.2.2.1 ILM Keying.         4.2.3 ILM Back Plate Design Overview         ILM Assembly         4.3.1 Manufacturing Assembly Flow         Processor Installation.         ILM Cover         Heatsink to ILM interface.         2011-0 Socket and ILM Electrical, Mechanical, and         ronmental Specifications.         Component Mass.         Package / Socket Stackup Height         Loading Specifications.         Electrical Requirements.         Environmental Requirements                             | 26<br>27<br>29<br>30<br>31<br>31<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>37<br>38<br>39<br>40<br>40 |

|   |      | 6.1.2          | Thermal<br>6.1.2.1 | Test Vehicle (TTV) T <sub>CASE</sub> and DTS Based Thermal Specifications<br>Thermal Specification |    |

|---|------|----------------|--------------------|----------------------------------------------------------------------------------------------------|----|

|   |      | 6.1.3          | Processo           | r Specification for Operation Where Digital Thermal Sensor Exceeds                                 |    |

|   |      | 6.1.4          | CONTROL            | Metrology                                                                                          | 43 |

|   | 6.2  |                |                    | hermal Features                                                                                    |    |

|   | 0.2  | 6.2.1          |                    | r Temperature                                                                                      |    |

|   |      | 6.2.2          |                    | Thermal Monitor                                                                                    |    |

|   |      | 0.2.2          | 6.2.2.1            | Frequency / SVID Control                                                                           | 45 |

|   |      |                | 6.2.2.2            | Clock Modulation                                                                                   | 46 |

|   |      | 6.2.3          |                    | and Mode                                                                                           |    |

|   |      | 6.2.4          |                    | T_N Signal                                                                                         |    |

|   |      | 6.2.5          |                    | RIP_N Signal                                                                                       |    |

|   | 6.3  |                |                    | ment Control Interface (PECI)                                                                      |    |

|   |      | 6.3.1          |                    | tion                                                                                               |    |

|   |      | 6.3.2          |                    | nt Capabilities                                                                                    |    |

|   | 6.4  | Fan Spe        |                    | ol with Digital Thermal Sensor                                                                     |    |

| 7 | DECL | Intorfo        |                    | -                                                                                                  | FO |

| / |      |                |                    |                                                                                                    |    |

|   | 7.1  | 7.1.1          |                    | ment Control Interface (PECI)                                                                      |    |

|   |      | /.1.1          | 7.1.1.1            | nt Capabilities<br>Thermal Management                                                              |    |

|   |      |                | 7.1.1.1            | Platform Manageability                                                                             |    |

|   |      |                | 7.1.1.2            | Processor Interface Tuning and Diagnostics                                                         | 51 |

|   |      | 7.1.2          |                    | mmand Suite                                                                                        |    |

|   |      | /              | 7.1.2.1            | Ping()                                                                                             |    |

|   |      |                | 7.1.2.2            | GetDIB()                                                                                           |    |

|   |      |                | 7.1.2.3            | GetTemp()                                                                                          | 55 |

|   |      |                | 7.1.2.4            | RdPkgConfig()                                                                                      |    |

|   |      |                | 7.1.2.5            | WrPkgConfig()                                                                                      |    |

|   |      |                | 7.1.2.6            | Package Configuration Capabilities                                                                 | 59 |

|   |      | 712            | 7.1.2.7            | Processor Thermal and Power Optimization Capabilities                                              |    |

|   |      | 7.1.3<br>7.1.4 |                    | Temperature Read                                                                                   |    |

|   |      | 7.1.4          | 7.1.4.1            | Notify Read/Write<br>Thermally Constrained Time Read                                               |    |

|   |      |                | 7.1.4.1            | Current Limit Read                                                                                 |    |

|   |      |                | 7.1.4.3            | Accumulated Energy Status Read                                                                     | 73 |

|   |      |                | 7.1.4.4            | Power Limit for the VCC Power Plane Write / Read                                                   |    |

|   |      |                | 7.1.4.5            | Package Power Limits For Multiple Turbo Modes                                                      | 74 |

|   |      |                | 7.1.4.6            | Socket Power Limit Performance Status Read                                                         |    |

|   |      |                | 7.1.4.7            | Socket Power-Performance Scalability Read                                                          | 75 |

|   |      |                | 7.1.4.8            | Socket Performance Indication Read                                                                 |    |

|   |      |                | 7.1.4.9            | RdIAMSR()<br>RdPCIConfig()                                                                         |    |

|   |      |                | 7.1.4.11           | RdPCIConfigLocal()                                                                                 | 82 |

|   |      |                | 7.1.4.12           | WrPCIConfigLocal()                                                                                 | 84 |

|   |      | 7.1.5          |                    | anagement                                                                                          |    |

|   |      |                | 7.1.5.1            | Power-up Sequencing                                                                                |    |

|   |      |                | 7.1.5.2            | Device Discovery                                                                                   | 87 |

|   |      |                | 7.1.5.3            | Client Addressing                                                                                  |    |

|   |      |                | 7.1.5.4            | C-states                                                                                           |    |

|   |      |                | 7.1.5.5            | S-states<br>Processor Reset                                                                        |    |

|   |      |                | 7.1.5.6<br>7.1.5.7 | Processor Reset<br>Processor Error Handling                                                        |    |

|   |      |                | 7.1.5.7            | Originator Retry and Timeout Policy                                                                | 90 |

|   |      |                | 7.1.5.9            | Enumerating PECI Client Capabilities                                                               |    |

|   |      | 7.1.6          | Multi-Do           | main Commands                                                                                      |    |

|   |      | 7.1.7          |                    | sponses                                                                                            |    |

|   |      |                | 7.1.7.1            | Abort FCS                                                                                          | 91 |

|   |      |                |                    |                                                                                                    |    |

|   |            | 7.1.7.2Completion Codes7.1.8Originator Responses7.1.9DTS Temperature Data7.1.9.1Format7.1.9.2Interpretation7.1.9.3Reserved Values | 92<br>93<br>93<br>93 |

|---|------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 8 | Theri      | nal Solutions                                                                                                                     | . 95                 |

|   | 8.1        | Performance Targets                                                                                                               |                      |

|   |            | 8.1.1 Reference Heatsink Assembly                                                                                                 |                      |

|   | 8.2        | Assembly Process for Reference Heatsinks                                                                                          |                      |

|   | 8.3        | Geometric Envelope for the Intel <sup>®</sup> Reference ATX Thermal Mechanical Design                                             |                      |

|   | 8.4        | Structural Considerations                                                                                                         |                      |

|   | 8.5<br>8.6 | Attachment to the ILM<br>Thermal Interface Material                                                                               |                      |

|   | 8.7        | Thermal Solution Performance                                                                                                      |                      |

|   | 0.7        | 8.7.1 Tall Heat Pipe Heatsink Performance                                                                                         |                      |

|   |            | 8.7.2 Liquid Cooling Thermal Solution Performance                                                                                 |                      |

|   | 8.8        | Thermal Design Guidelines                                                                                                         |                      |

|   |            | 8.8.1 Intel <sup>®</sup> Turbo Boost 2 Technology                                                                                 | 100                  |

|   |            | 8.8.2 Thermal Characterization Parameter                                                                                          | 101                  |

|   |            | 8.8.3 Fan Speed Control                                                                                                           | 102                  |

| 9 | Quali      | ty and Reliability Requirements                                                                                                   | 103                  |

|   | 9.1        | Use Conditions                                                                                                                    |                      |

|   | 9.2        | Intel <sup>®</sup> Reference Component Validation                                                                                 | 104                  |

|   |            | 9.2.1 Board Functional Test Sequence                                                                                              |                      |

|   |            | 9.2.2 Post-Test Pass Criteria Examples                                                                                            |                      |

|   |            | 9.2.3 Recommended BIOS/Processor/Memory Test Procedures                                                                           |                      |

|   | 9.3        | Material and Recycling Requirements                                                                                               | 105                  |

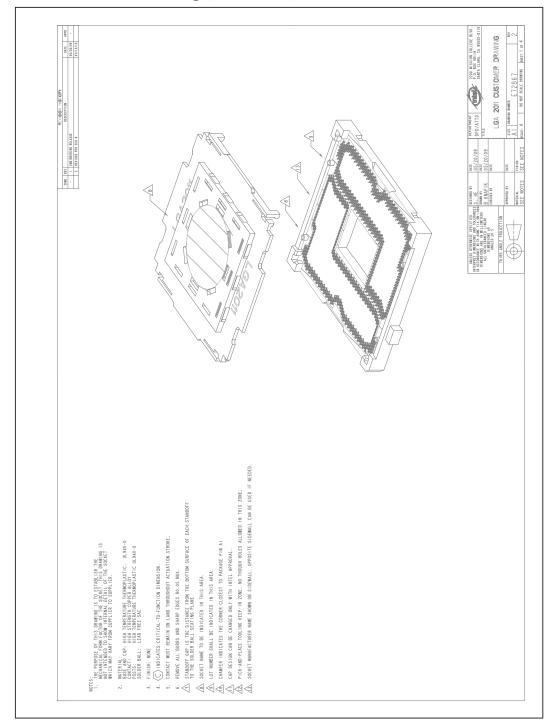

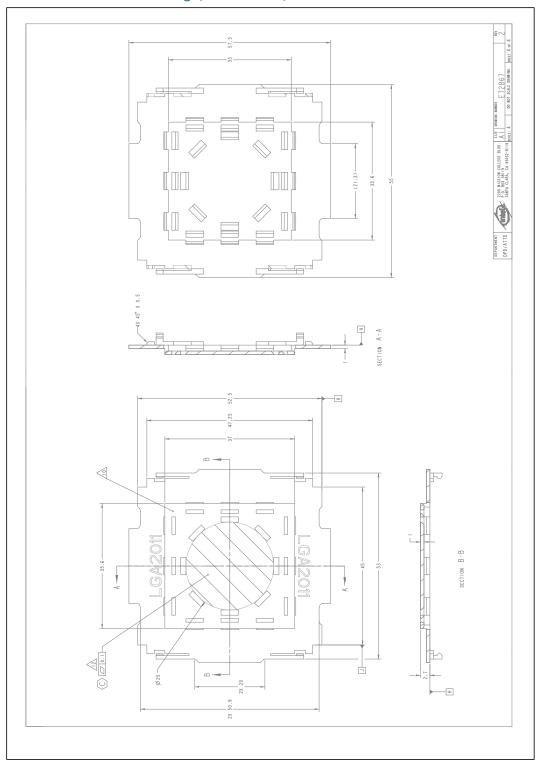

| Α | Mech       | anical Drawings                                                                                                                   | 107                  |

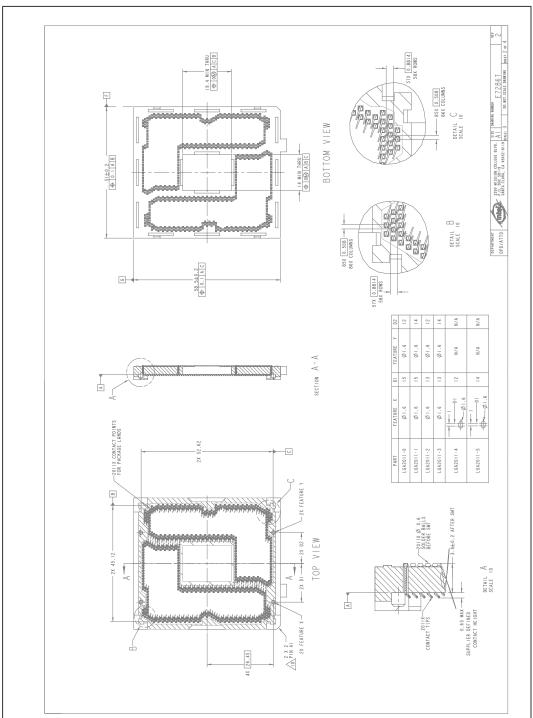

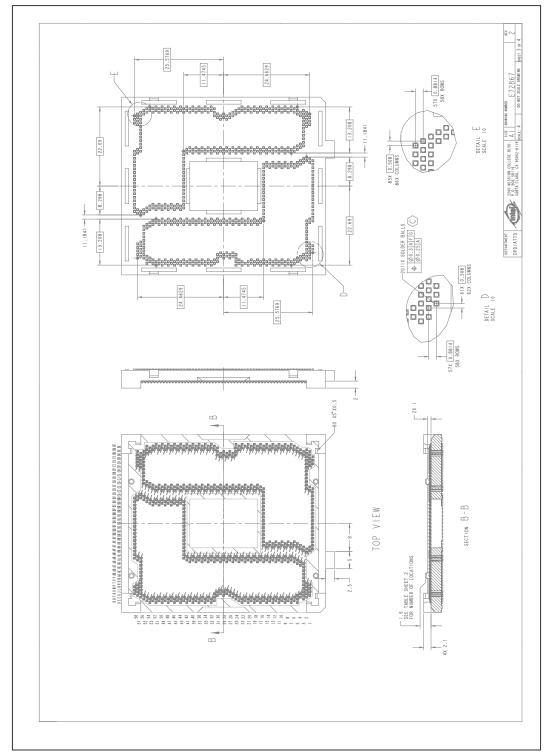

| в | Sock       | et Mechanical Drawings                                                                                                            | 110                  |

| С | Com        | oonent Suppliers                                                                                                                  | 115                  |

|   | C.1        | Intel Enabled Supplier Information                                                                                                | 115                  |

|   |            | C.1.1 Intel Reference or Collaboration Thermal Solutions                                                                          | 115                  |

|   |            | C.1.2 Socket and ILM Components                                                                                                   | 116                  |

| D | Pack       | age Mechanical Drawings                                                                                                           | 117                  |

## **Figures**

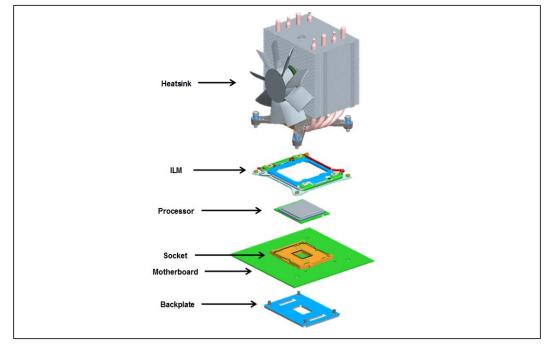

| 1-1         | Platform LGA2011-0 Socket Stack with Tall-Heat Pipe Heatsink     |      |

|-------------|------------------------------------------------------------------|------|

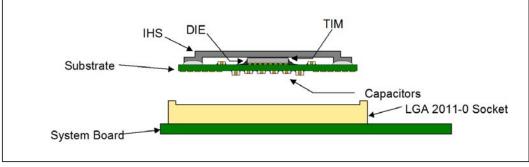

| 2-1         | Processor Package Assembly Sketch                                |      |

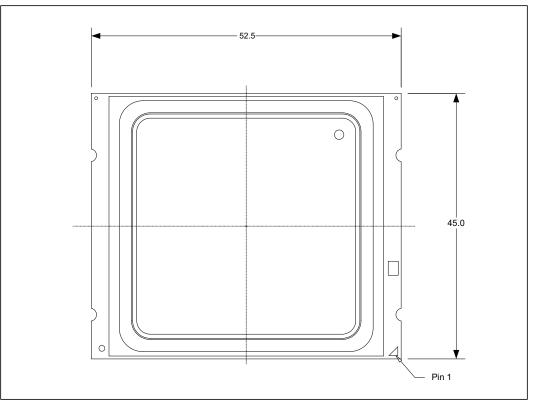

| 2-2         | Package View                                                     | . 14 |

| 2-3         | Processor Top-Side Markings                                      | . 16 |

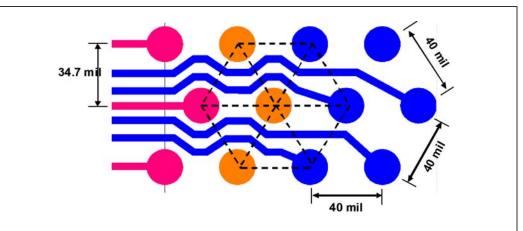

| 3-1         | Hexagonal Array in LGA2011-0                                     |      |

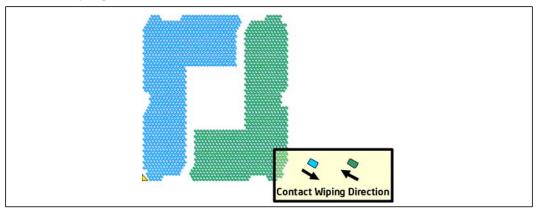

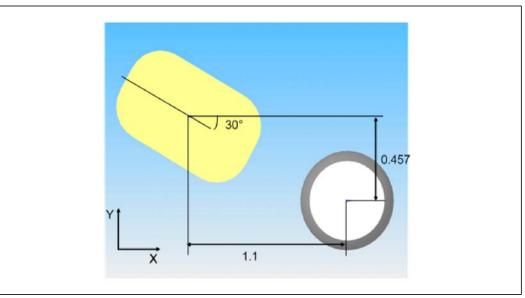

| 3-2         | Contact Wiping Direction                                         | . 18 |

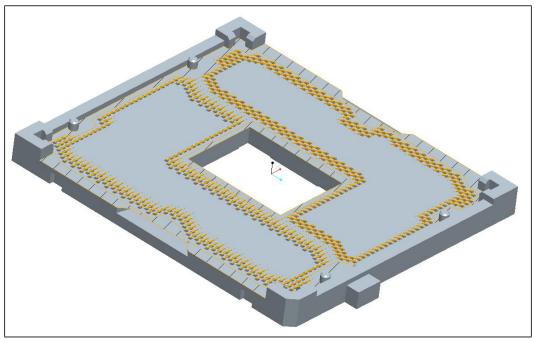

| 3-3         | Schematic of LGA2011-0 Socket with Pick and Place Cover Removed  | . 18 |

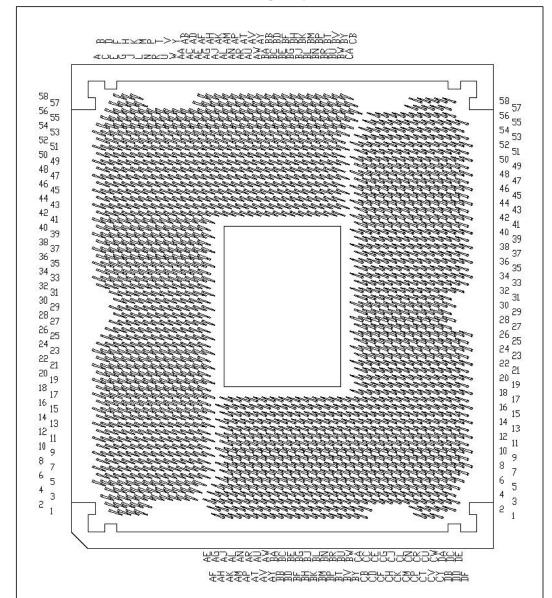

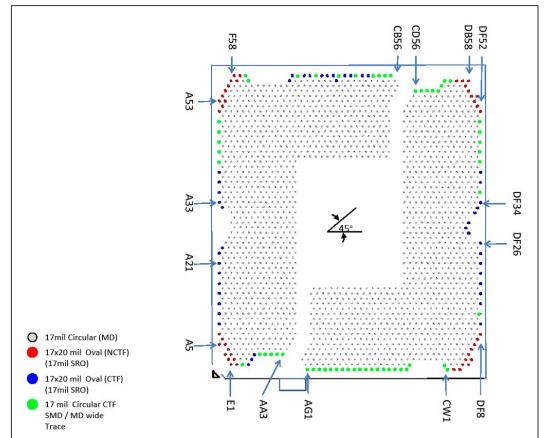

| 3-4         | LGA2011-0 Socket Contact Numbering (Top View of Socket)          | . 19 |

| 3-5         | Offset between LGA Land Center and Solder Ball Center            |      |

| 3-6         | LGA2011-0 Socket Land Pattern (Top View of Board)                |      |

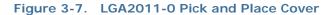

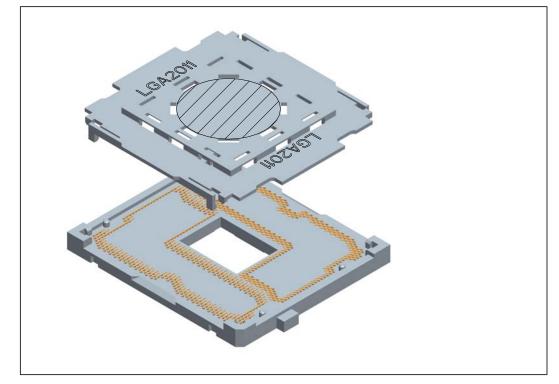

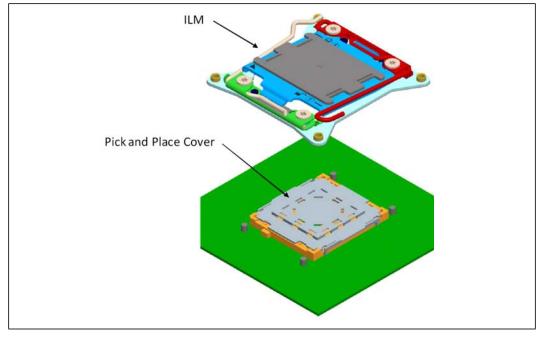

| 3-7         | LGA2011-0 Pick and Place Cover                                   |      |

| 3-8         | Pick and Place Cover                                             |      |

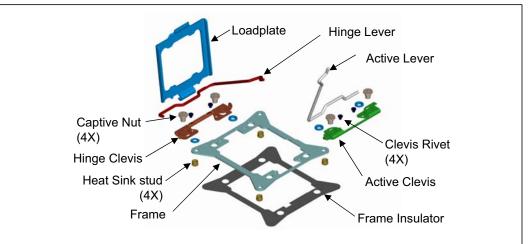

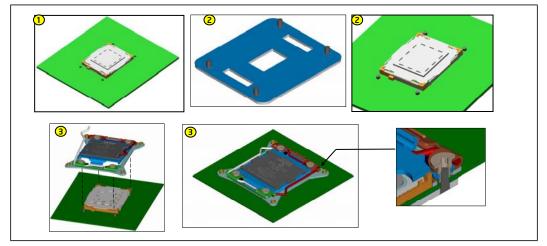

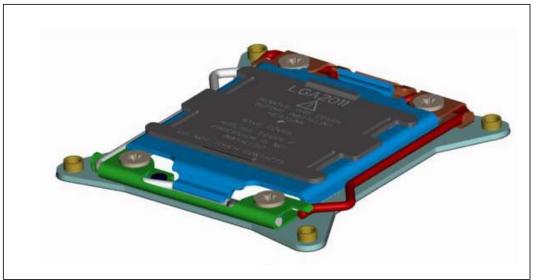

| 4-1         | Square ILM Part Terminology                                      |      |

| 4-2         | Square ILM Assembly                                              |      |

| 4-3         | ILM as Universal Retention Mechanism                             |      |

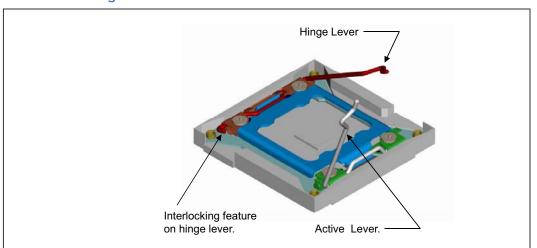

| 4-4         | ILM Interlocking Feature                                         |      |

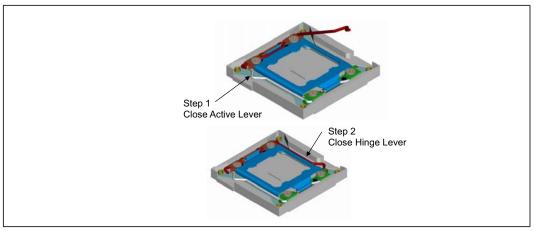

| 4-5         | ILM Lever Closing Sequence                                       |      |

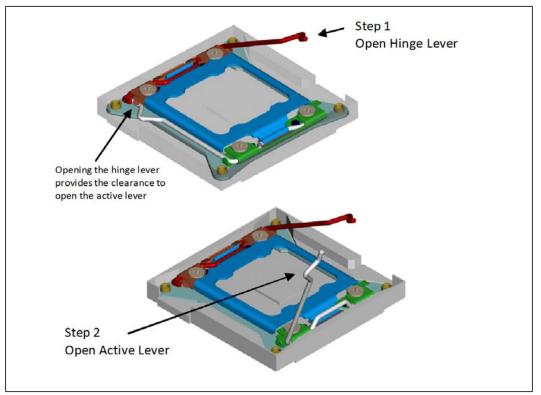

| 4-6         | Opening ILM.                                                     |      |

| 4-7         | Opening Sequence for ILM and Load Plate (continued)              | . 31 |

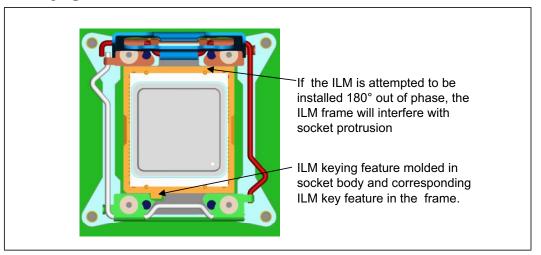

| 4-8         | ILM Keying                                                       |      |

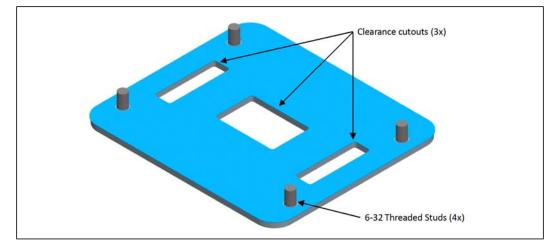

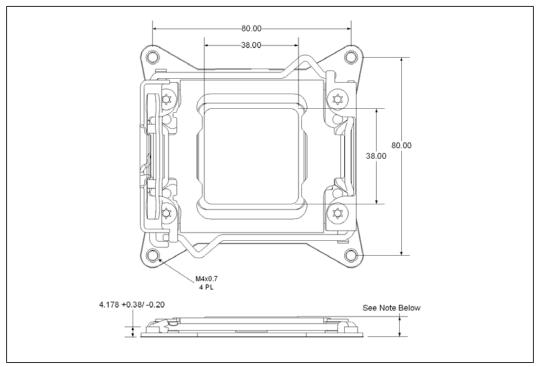

| 4-9         | ILM Back Plate                                                   |      |

| 4-10        | Assembling Socket, Back Plate, and ILM onto the Motherboard      |      |

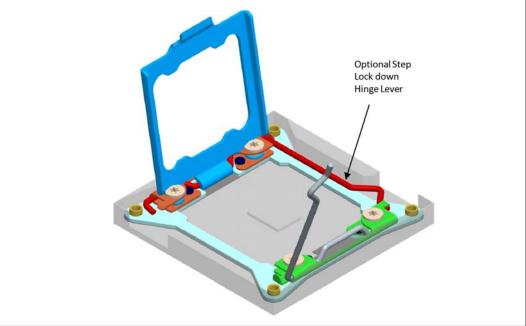

| 4-11        | Optional Step: Lock down the Hinge Lever                         |      |

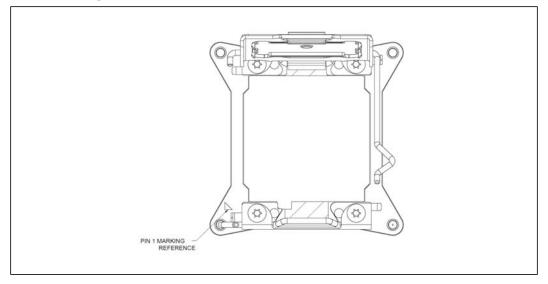

| 4-12        | Pin 1 Markings on the ILM Frame                                  |      |

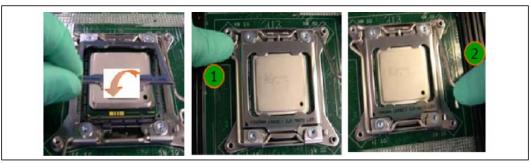

| 4-13        | Closing ILM and Load Plate                                       |      |

| 4-14        | ILM with Cover                                                   |      |

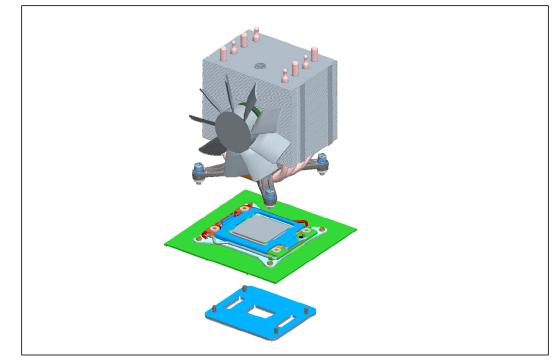

| 4-15        | Heatsink to ILM Interface                                        |      |

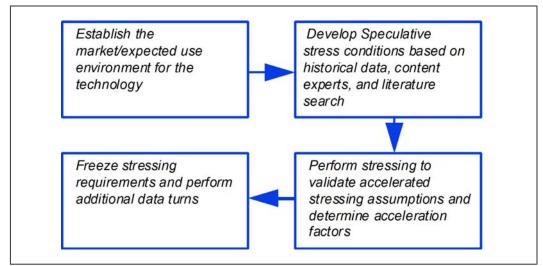

| 4-15<br>5-1 | Flow Chart of Knowledge-Based Reliability Evaluation Methodology |      |

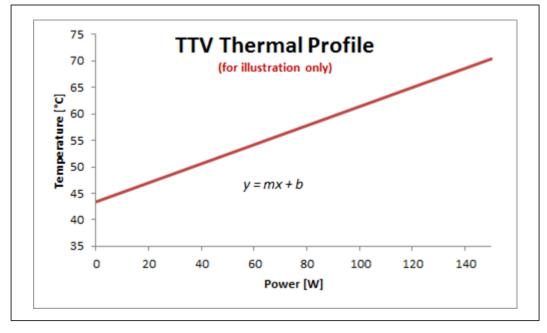

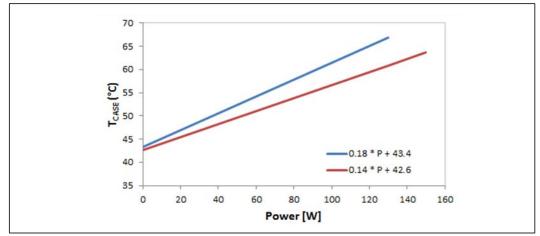

| 5-1<br>6-1  | Typical Thermal Profile Graph (Illustration Only)                |      |

| 6-2         | T <sub>CASE</sub> Thermal Profile                                |      |

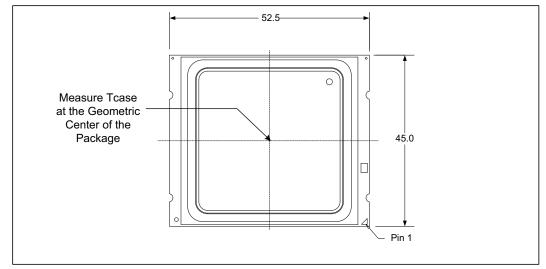

| 0-2<br>6-3  | Case Temperature (T <sub>CASE</sub> ) Measurement Location       |      |

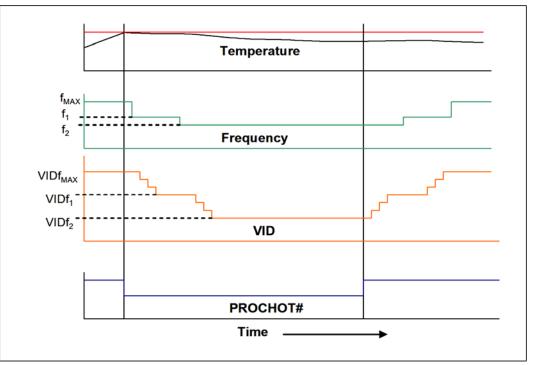

| 6-3<br>6-4  | Frequency and Voltage Ordering                                   | . 44 |

|             |                                                                  |      |

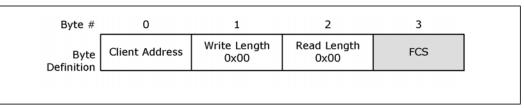

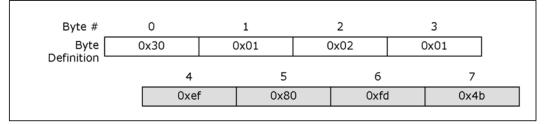

| 7-1<br>7-2  | Ping()                                                           |      |

|             | Ping() Example                                                   |      |

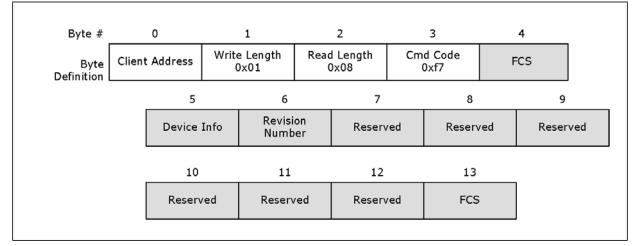

| 7-3         | GetDIB()                                                         |      |

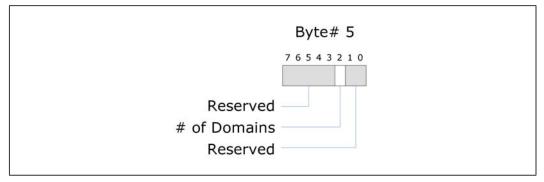

| 7-4         | Device Info Field Definition                                     |      |

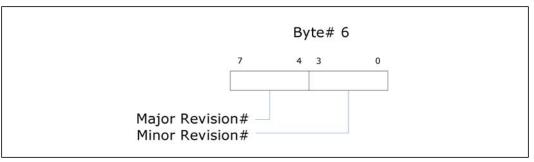

| 7-5         | Revision Number Definition                                       |      |

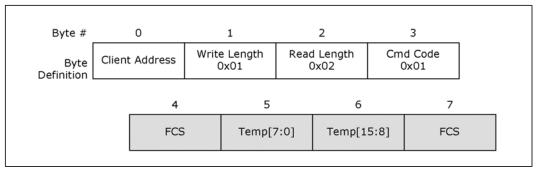

| 7-6         | GetTemp()                                                        |      |

| 7-7         | GetTemp() Example                                                |      |

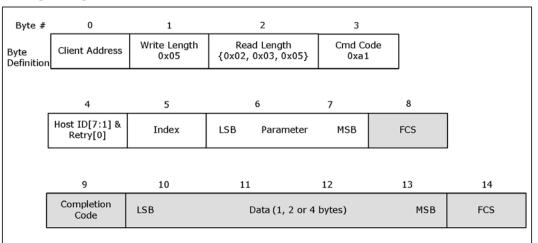

| 7-8         | RdPkgConfig()                                                    | . 5/ |

| 7-9         | WrPkgConfig()                                                    |      |

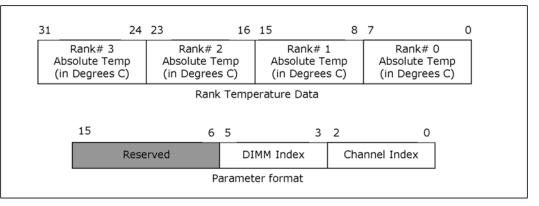

| 7-10        | DRAM Thermal Estimation Configuration Data                       |      |

| 7-11        | DRAM Rank Temperature Write Data                                 |      |

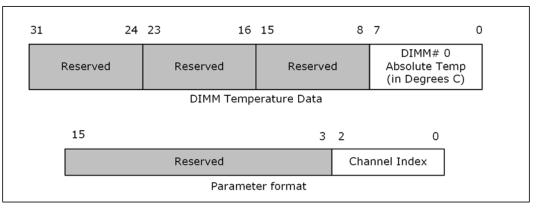

| 7-12        | DIMM Temperature Read / Write                                    |      |

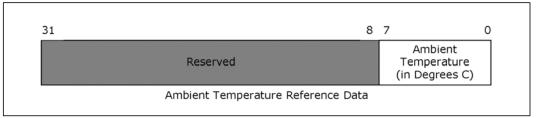

| 7-13        | Ambient Temperature Reference Data                               |      |

| 7-14        | DRAM Channel Temperature                                         | . 63 |

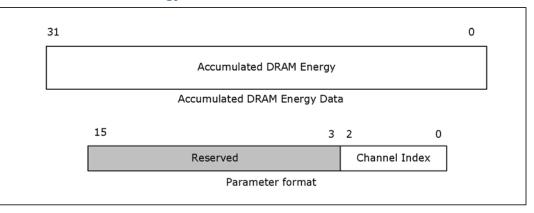

| 7-15        | Accumulated DRAM Energy Data                                     |      |

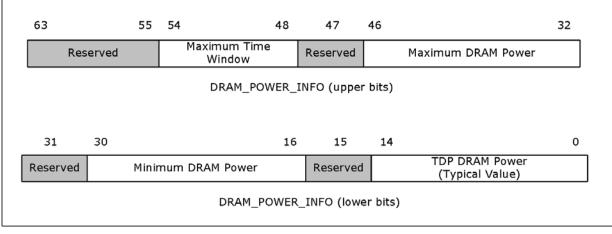

| 7-16        | DRAM Power Info Read Data                                        |      |

| 7-17        | DRAM Power Limit Data                                            |      |

| 7-18        | DRAM Power Limit Performance Data                                |      |

| 7-19        | CPUID Data                                                       |      |

| 7-20        | Platform ID Data                                                 |      |

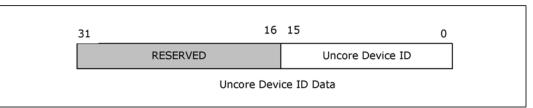

| 7-21        | Uncore Device ID                                                 |      |

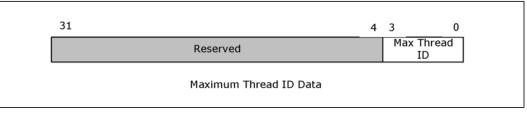

| 7-22        | Maximum Thread ID                                                |      |

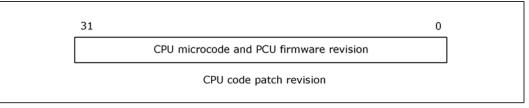

| 7-23        | Processor Microcode Revision                                     | . 69 |

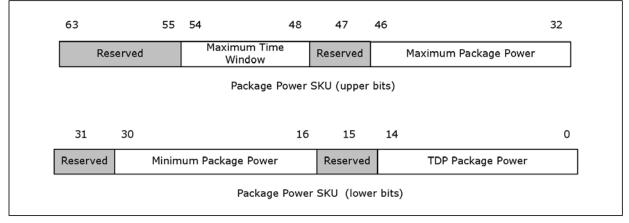

| 7-24 | Package Power SKU Unit Data                                | . 69 |

|------|------------------------------------------------------------|------|

| 7-25 | Package Power SKU Data                                     | . 70 |

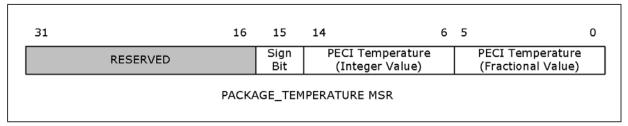

| 7-26 | Package Temperature Read Data                              | .71  |

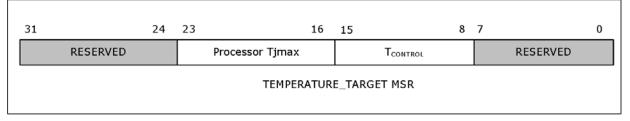

| 7-27 | Temperature Target Read                                    | .71  |

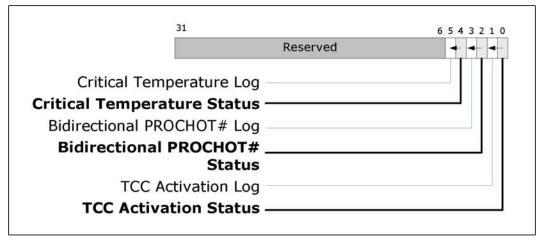

| 7-28 | Thermal Status Word                                        | . 72 |

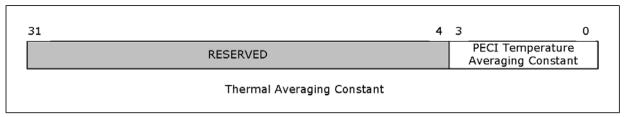

| 7-29 | Thermal Averaging Constant Write / Read                    | .72  |

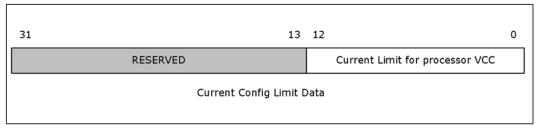

| 7-30 | Current Config Limit Read Data                             | .73  |

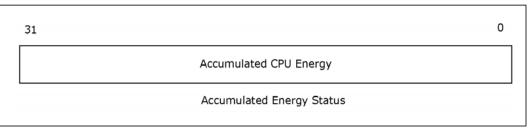

| 7-31 | Accumulated Energy Read Data                               | . 73 |

| 7-32 | Power Limit Data for VCC Power Plane                       | .74  |

| 7-33 | PKG_TURBO_POWER_LIMIT Data                                 | .74  |

| 7-34 | Socket Power Limit Performance Data                        | . 75 |

| 7-35 | Socket Power-Performance Scalability Data                  | .75  |

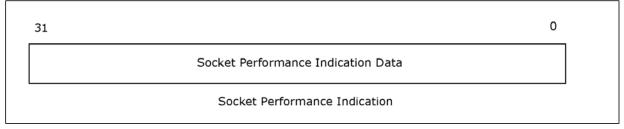

| 7-36 | Socket Performance Indication Data                         | . 75 |

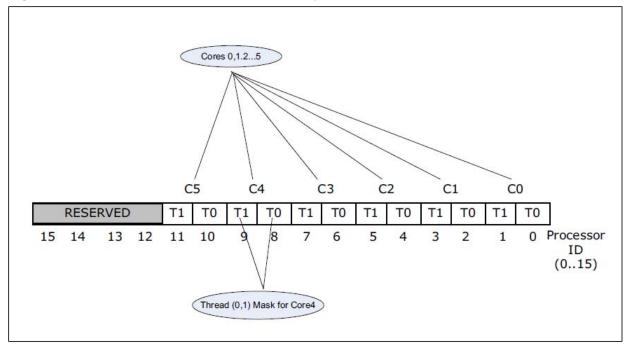

| 7-37 | Processor ID Construction Example                          | .77  |

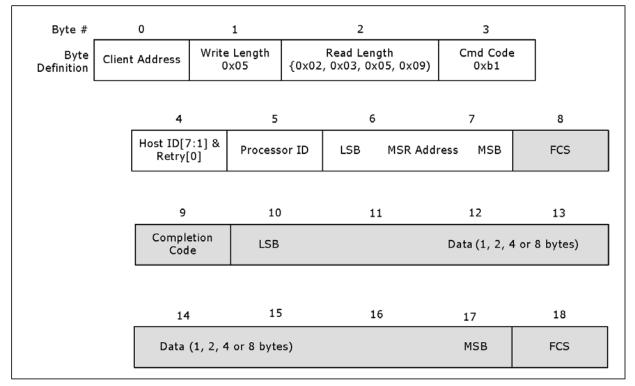

| 7-38 | RdIAMSR()                                                  | .77  |

| 7-39 | PCI Configuration Address                                  | . 80 |

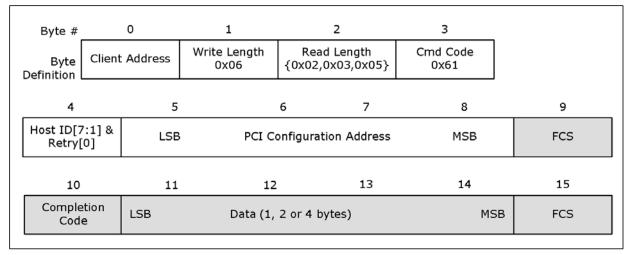

| 7-40 | RdPCIConfig()                                              | .81  |

| 7-41 | PCI Configuration Address for Local Accesses               | . 82 |

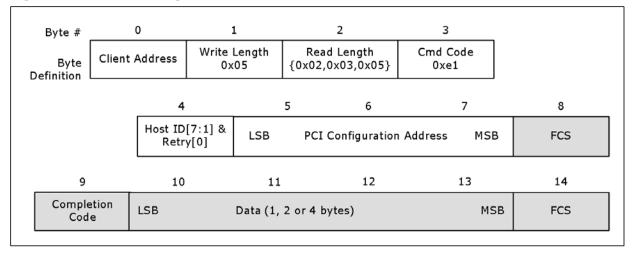

| 7-42 | RdPCIConfigLocal()                                         |      |

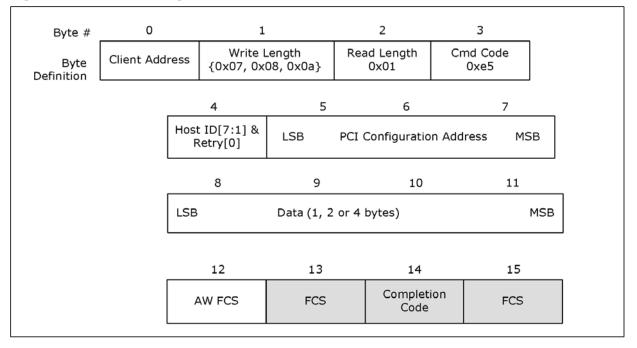

| 7-43 | WrPCIConfigLocal()                                         | . 85 |

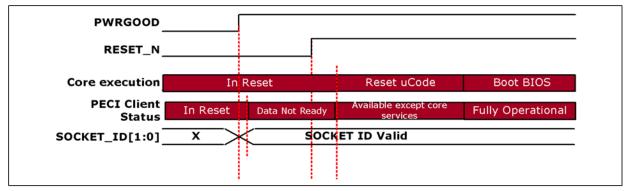

| 7-44 | The Processor PECI Power-up Timeline()                     |      |

| 7-45 | Temperature Sensor Data Format                             | . 93 |

| 7-46 | Temperature Filtering                                      | . 93 |

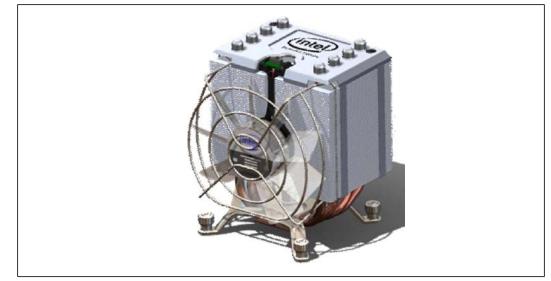

| 8-1  | Radial Fin Heatsink Assembly                               | .95  |

| 8-2  | Tall Heat Pipe Heatsink Assembly                           |      |

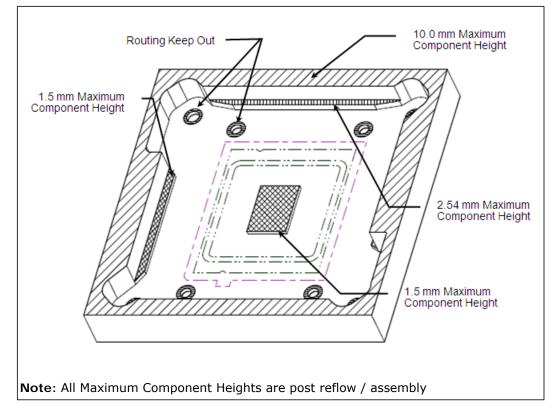

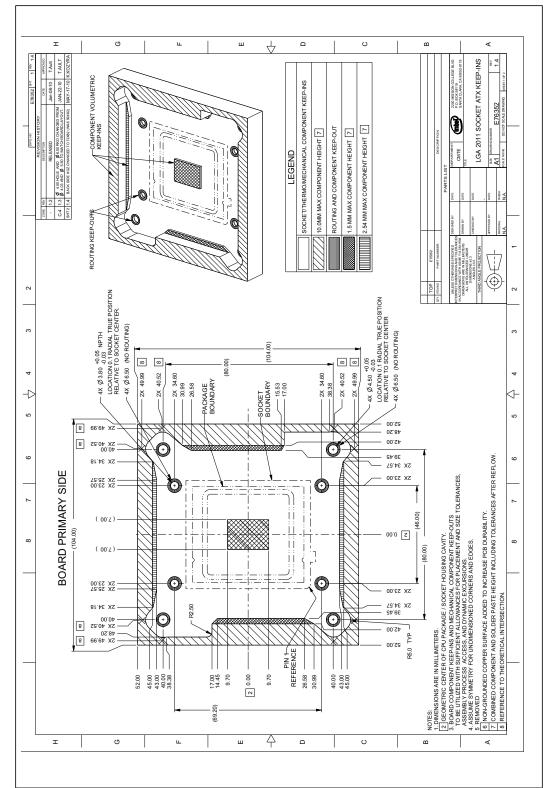

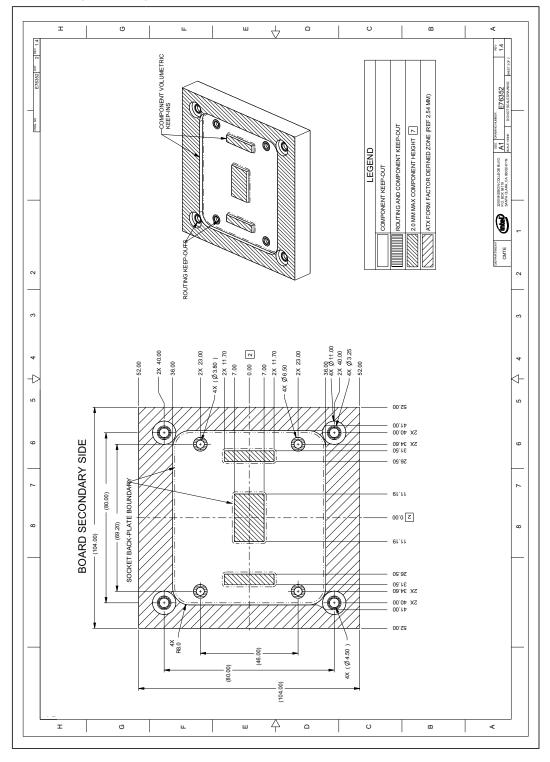

| 8-3  | ATX KOZ 3-D Model Primary (Top) Side                       |      |

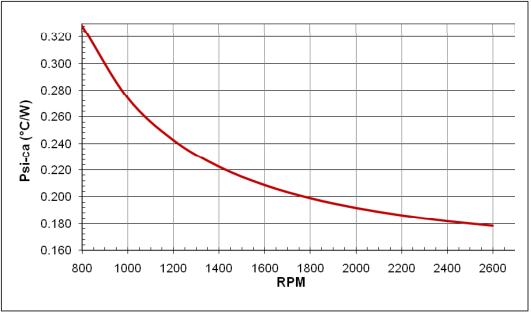

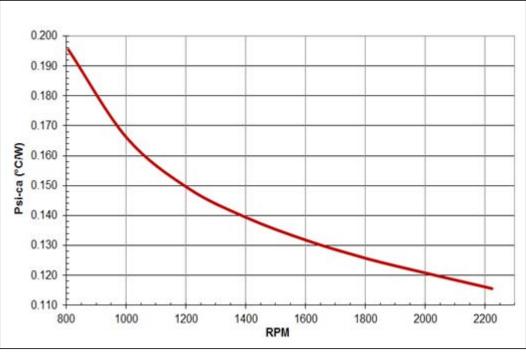

| 8-4  | T-HPHS Psi-ca versus RPM                                   |      |

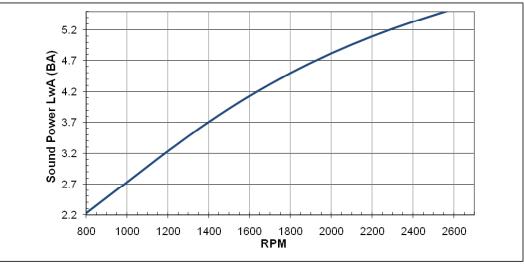

| 8-5  | T-HPHS Sound Power (BA) versus RPM                         |      |

| 8-6  | RTS2011LC Psi-ca versus RPM                                |      |

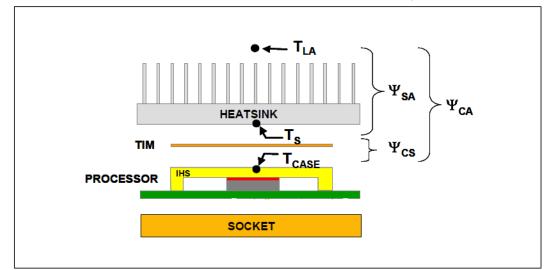

| 8-7  | Processor Thermal Characterization Parameter Relationships | 101  |

# Tables

| 1-1  | Terms and Descriptions                                                 |    |

|------|------------------------------------------------------------------------|----|

| 1-2  | Related Documents                                                      | 12 |

| 2-1  | Processor Loading Specifications                                       | 15 |

| 2-2  | Package Handling Guidelines                                            | 15 |

| 2-3  | Processor Materials                                                    | 16 |

| 3-1  | LGA2011-0 Socket Attributes                                            | 17 |

| 4-1  | Square ILM Assembly Component Thickness and Material                   | 28 |

| 5-1  | Socket and Retention Component Mass                                    | 37 |

| 5-2  | 2011-land Package and LGA2011-0 Socket Stackup Height                  | 37 |

| 5-3  | Socket and ILM Mechanical Specifications                               | 38 |

| 5-4  | Electrical Requirements for LGA2011-0 Socket                           | 39 |

| 6-1  | Processor Thermal Specifications                                       | 42 |

| 7-1  | Summary of Processor-specific PECI Commands                            | 50 |

| 7-2  | Minor Revision Number Meaning                                          | 54 |

| 7-3  | GetTemp() Response Definition                                          | 56 |

| 7-4  | RdPkgConfig() Response Definition                                      | 57 |

| 7-5  | WrPkgConfig() Response Definition                                      | 59 |

| 7-6  | RdPkgConfig() & WrPkgConfig() DRAM Thermal Services Summary            | 60 |

| 7-7  | Channel and DIMM Index Decoding                                        | 61 |

| 7-8  | RdPkgConfig() & WrPkgConfig() Processor Thermal and Power Optimization |    |

|      | Services Summary                                                       | 65 |

| 7-9  | Platform ID Encoding                                                   | 68 |

| 7-10 | Power Control Register Unit Calculations                               | 70 |

| 7-11 | RdIAMSR() Response Definition                                 | 78  |

|------|---------------------------------------------------------------|-----|

| 7-12 | RdIAMSR() Services Summary                                    | 78  |

| 7-13 | RdPCIConfig() Response Definition                             | 81  |

| 7-14 | RdPCIConfigLocal() Response Definition                        | 83  |

| 7-15 | WrPCIConfigLocal() Response Definition                        | 85  |

| 7-16 | WrPCIConfigLocal() Memory Controller Device/Function Support  |     |

| 7-17 | PECI Client Response During Power-Up                          | 86  |

| 7-18 | SOCKET ID Strapping                                           | 87  |

| 7-19 | Power Impact of PECI Commands versus C-states                 | 88  |

| 7-20 | Domain ID Definition                                          | 90  |

| 7-21 | Multi-Domain Command Code Reference                           | 91  |

| 7-22 | Completion Code Pass/Fail Mask                                |     |

| 7-23 | Device Specific Completion Code (CC) Definition               | 91  |

| 7-24 | Originator Response Guidelines                                | 92  |

| 7-25 | Error Codes and Descriptions                                  | 94  |

| 8-1  | Processor Reference Thermal Boundary Conditions               |     |

| 8-2  | Reference Heatsink Clearance above the Motherboard            | 97  |

| 8-3  | Intel <sup>®</sup> reference thermal solution TIM             |     |

| 8-4  | Fan Speed Control, T <sub>CONTROL</sub> and DTS Relationship1 | .02 |

| 9-1  | Use Conditions Environment (System Level)1                    | .03 |

| 9-2  | Use Conditions Environment (System Level)1                    |     |

# **Revision History**

| Revision<br>Number | Description                                                                                                                                                                                                                                                                                 | Revision Date     |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 001                | Initial release of the document                                                                                                                                                                                                                                                             | November 2011     |

| 002                | <ul> <li>Added Desktop Intel<sup>®</sup> Core<sup>™</sup> i7-3970X Extreme Edition Processor</li> <li>Updated EOL loading specification and added note that BOL minimum load is for guidance only, in Section 5.4,</li> </ul>                                                               | November 2012     |

| 003                | <ul> <li>Added Desktop Intell<sup>®</sup> Core™ i7-4960X Extreme Edition Processor Series for the LGA2011<br/>Socket</li> <li>Added Desktop Intell<sup>®</sup> Core™ i7-49xx and i7-48xx Processor Series for the LGA2011<br/>Socket</li> <li>Minor edits throughout for clarity</li> </ul> | September<br>2013 |

| 004                | Updated Table 6-1, Processor Thermal Specifications                                                                                                                                                                                                                                         | November 2013     |

### §§

This document provides guidelines for the design of thermal and mechanical solutions for 1-socket High End Desktop (HEDT) processors in the platform. The processors covered in this TMSDG are listed in the Datasheet (see Table 1-2) and include the following:

- Intel<sup>®</sup> Core<sup>™</sup> i7 Processor Family Datasheet (Document #326196)

- Intel<sup>®</sup> Core<sup>™</sup> i7-3970X processor Extreme Edition

- Intel<sup>®</sup> Core<sup>™</sup> i7-3960X processor Extreme Edition

- Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor

- Intel<sup>®</sup> Core<sup>™</sup> i7-3820 processor

- Intel<sup>®</sup> Core<sup>™</sup> i7 Processor Family Datasheet (Document #329366)

- Intel<sup>®</sup> Core<sup>™</sup> i7-4960X processor Extreme Edition

- Intel<sup>®</sup> Core<sup>™</sup> i7-4930K processor

- Intel<sup>®</sup> Core<sup>™</sup> i7-4820K processor