Video Processing

# Tone Mapping Operator (TMO) Intel® FPGA IP

# Tone Mapping Operator (TMO) Intel® FPGA IP corrects poorly exposed images and video to reveal invisible detail.

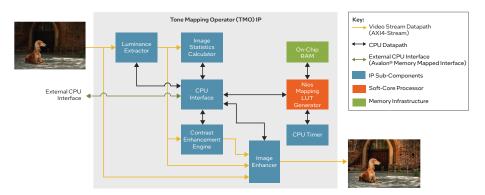

The TMO Intel FPGA IP modifies the contrast of a video stream to improve visibility in a wide variety of applications, such as medical imaging, video conferencing, daylight projection, security cameras, and machine vision. The IP is tile-based to take account of local exposure variations, improving the visibility of latent image detail to enhance and ease the overall viewing experience.

The TMO IP core accepts RGB-format video input as an AXI4-Stream, statistically analyzes the image luminance (locally and globally) and dynamically adjusts image components to improve overall image contrast. These operations enhance underexposed and overexposed imagery to fully utilize the available dynamic range.

The TMO IP requires an external processor, such as the Nios® II processor FPGA soft core, to allow configuration of TMO IP blocks and take measurements via the register bus.

# **Applications**

Tone mapping adds real advantage in a range of applications including:

- Automotive imaging

- Medical imaging

- Video projection

- · Security cameras

- Video conferencing

- · Machine vision

#### **Key Features**

- · Multi-tile local image statistics analysis

- · Support for 8, 10 and 12 bit per color component

- · Support up to 4 pixels in parallel per clock processing

- · Low subframe latency (~ 100 clock cycles)

- Support resolutions up to 4K at 60 fps on Intel®C10/A10/ S10 FPGAs and up to 8K at 60 fps on Intel Agilex® FPGAs

- · Low FPGA resource utilisation

- AXI4-Stream video I/O interface

- AXI4-Stream ↔ Avalon-Stream Protocol Converters

- Avalon® Memory-Mapped CPU control and memory interfaces

#### **Customer Benefits**

- Low resource yielding lower power 'Edge' implementations

- Free Intel® FPGA Evaluation Mode

- Design example available in Intel Resource and Design Center

- · Avalon® or AXI interfaces

- · Fully maintained and supported by Intel

#### **Supported Devices**

The TMO IP can be implemented on the following Intel FPGAs:

- Intel® Cyclone® 10 GX FPGAs

- Intel<sup>®</sup> Arria<sup>®</sup> 10 FPGAs

- Intel® Stratix® 10 FPGAs

- Intel Agilex® FPGAs

#### **Design Your Product Today with Intel FPGAs**

Intel provides a large range of complementary and modular IP cores for video processing and connectivity. These IP cores can be used to create complete solutions for applications in Studio Broadcast, ProAV, Aerospace/Defense, Medical, Consumer, Automotive, Machine vision, and more.

More information is available about Intel video IP at www.intel. com/content/www/us/en/broadcast/products/programmable/overview.html or contact an Intel sales representative.

## **Design Example**

Intel® Arria® 10 GX FPGA Development Kit with Bitec HDMI FMC daughter card. Fully compatible with Intel IP cores.

### Typical Resource Use

| Format               | ALMs    | M20K | DSPs |

|----------------------|---------|------|------|

| HD (1,920 x 1,080p)  | ~7,000  | 230  | 36   |

| UHD (3,840 x 2,160p) | ~10,000 | 465  | 72   |

#### **Useful Links**

- Intel FPGA Tone Mapping Operator (TMO) Design Example

Requires Intel Resource & Design Center access

- Intel® Arria® 10 GX FPGA Development Kit

- Intel® Cyclone® 10 GX FPGA Development Kit

- Intel® Stratix® 10 GX FPGA Development Kit

- Intel Agilex® 7 FPGA Development Kit

- Bitec HDMI FMC daughter card

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

SS-1139-1.2

2