Devido a um problema com o Intel® FPGA Power and Thermal Calculator (PTC) no software Intel® Quartus® Prime Pro Edition versão 20.3 e anterior, você pode ver este erro, mesmo que ainda haja pinos disponíveis quando pinos de entrada diferenciais são usados e as tensões vcCIO de todos os bancos de E/S não são 2,5V em Intel® Stratix® 10 dispositivos.

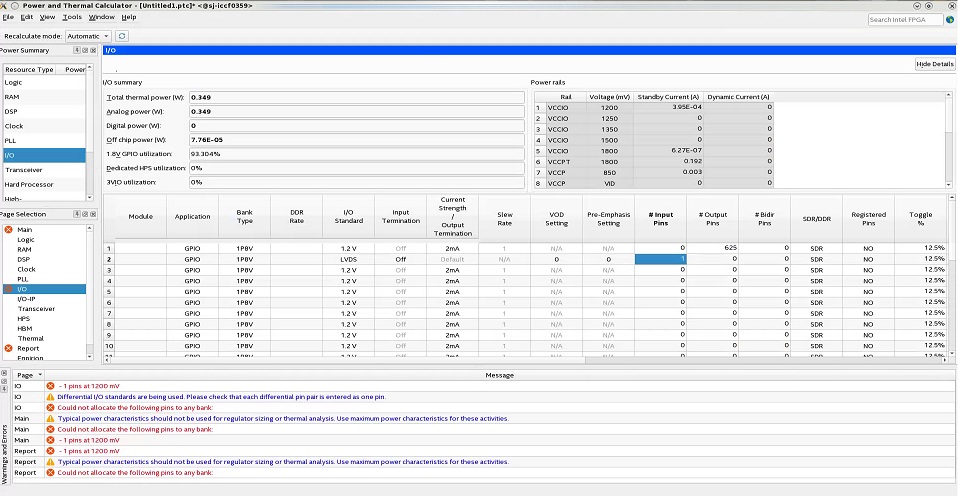

Aqui está um exemplo.

Dispositivo: 1SG280H

Pacote: F50

Número de E/S do usuário: 672

Número de banco de E/S: 14

Número do banco de E/S pré-E/S do pino: 48

Uso de E/S do usuário:

Saída de 1,2 V * 625 pinos

Entrada LVDS * 1 par

Neste caso, uma vez que 625 pinos são usados para saída de 1,2 V, as tensões vcCIO de 14 bancos de E/S são de 1,2 V.

A entrada LVDS é alimentada por VCCPT, não VCCIO. Assim, um par de entradas LVDS deve ser capaz de ser atribuído aos pinos restantes, mas o PTC exibe incorretamente um erro, conforme mostrado na imagem a seguir.

Você pode ignorar com segurança este erro.

Este problema é corrigido a partir do Intel® FPGA Power and Thermal Calculator (PTC) no software Intel® Quartus® Prime Pro Edition versão 21.3.