Após o Intel® Stratix® 10 concluir a configuração e entrar no modo do usuário, você deve implementar uma sequência de reinicialização antes de executar sua aplicação. Após a conclusão do estágio de configuração, as funções do dispositivo Intel Stratix 10 não devem entrar no modo de usuário simultaneamente. Quando o dispositivo entra no modo de usuário, um clock de execução gratuito pode causar uma condição de corrida de clock entre as lógicas do usuário que corrompe as condições iniciais do dispositivo.

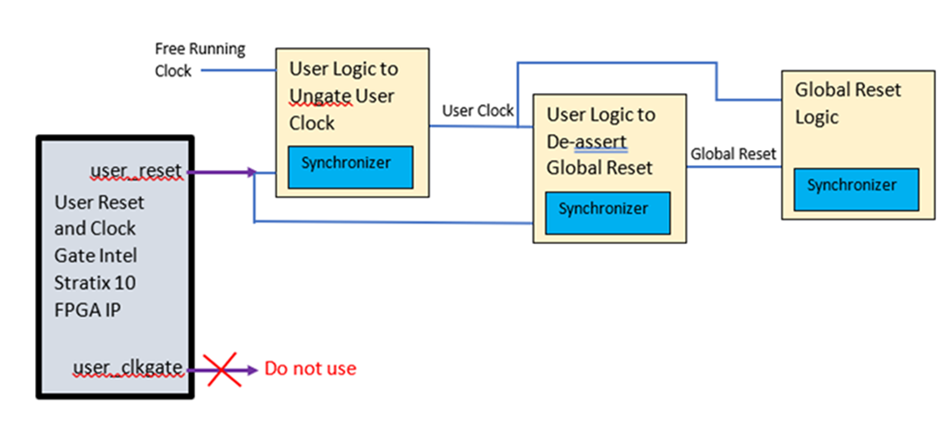

Para evitar este evento, a Intel recomenda que você construa um projeto usando o User Reset and Clock Gate Intel Stratix 10 FPGA IP com sua própria lógica do usuário para desajustar o Clock do usuário e desafirmar o sinal de redefinição global, conforme mostrado na Figura 1. Use o núcleo ip Intel Stratix de reset e clock Intel Stratix 10 FPGA para desafirmar o sinal da porta user_reset para desarmá-lo. Em seguida, construa sua própria lógica para desafirmar o sinal de redefinição global após ter desajustado o clock do usuário.

Observe que o Clock de execução livre é um clock de origem externa, enquanto o Clock do usuário é um clock que marca a lógica do usuário no FPGA. O Clock do usuário também pode ser um clock de execução gratuito ou um clock de loop bloqueado por fase (PLL).

Espera-se que apenas uma única instância de IP seja necessária para desajustar todos os clocks do usuário, enquanto o sinal de redefinição global deve ser usado para liberar/desafirmar a reinicialização em vários domínios. Se o projeto tiver vários domínios de redefinição, certifique-se de que o sinal de redefinição global está mantido por tempo suficiente para que o sinal se propague a todos os domínios antes de desafirmá-lo.

Figura 1. Diagrama do bloco de reinicialização e de gating de clock do usuário

Nota: Não use a porta user_clkgate do User Reset e Clock Gate Intel Stratix 10 FPGA IP.

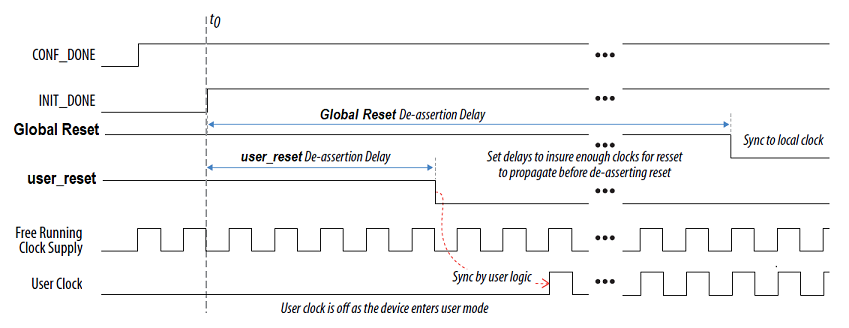

Atraso recomendado de desafirmação para sinal user_reset usando o Intel Stratix 10 FPGA user Reset and Clock Gate IP e o atraso de desafirmação para o sinal de redefinição global

O user_reset de desafirmação do sinal deve ter mais de um ciclo de clock do usuário. Você pode obter o atraso desejado, inserindo o valor De-assertion Delay no User Reset and Clock Gate Intel Stratix 10 FPGA IP. Os valores possíveis para o parâmetro De-assertion Delay no User Reset and Clock Gate Intel Stratix 10 FPGA IP podem variar de 0 ns a 65.535 ns. Você deve construir um sincronizador usando a técnica anti-metástil padrão dentro:

- A lógica do usuário para ungar o clock do usuário para sincronizar o sinal user_reset em relação ao clock de execução gratuito.

- A lógica do usuário para desafirmar o reset global para sincronizar o sinal user_reset em relação ao Clock do usuário.

O atraso de desafirmação do sinal de reinicialização global deve ser longo o suficiente para que o sinal de redefinição global se propague para a lógica de redefinição global em seu sistema após a execução do ClocK do usuário. Construa sua própria lógica do usuário para desafirmar o sinal de redefinição global após user_reset a ser desafirmado e o Clocdo usuário K estiver sendo executado. Você também deve sincronizar o sinal de redefinição global em relação ao Clock do usuário usando técnicas anti-metastable padrão.

Figura 2. Diagrama de sincronização de reinicialização e de gaagem de clock do usuário

Essas informações estão documentadas no guia de usuário de configuração Intel Stratix 10 mais recente para o software Intel® Quartus® Prime Pro Edition v19.1.