Devido a um problema no software Intel® Quartus® Prime Pro Edition v21.4, um projeto de F-tile PMA/FEC Direct PHY Intel® FPGA IP contendo transceptores FGT ou FHT pode incorretamente mostrar falhas de sincronização relacionadas ao controlador de reinicialização suave (SRC).

As características dessas falhas de sincronização são que o lançamento ou o clock de trava serão listados como src_divided_osc_clk. O outro relógio (o relógio de trava ou o relógio de lançamento) será um relógio diferente.

Você também pode ver que a folga relatada é um número negativo muito grande, na ordem de -90 ns.

Exemplos dessas falhas de sincronização são os seguintes:

Exemplo de falha de sincronização 1

Do nó: IP_INST[0].hw_ip_top|dut|eth_f_0|sip_inst|sip_freeze_tx_src_reg[0]

Nó: eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl_sync|sip_freeze_tx_SRC_sequence_inst[18]|din_s1

Clock de lançamento: reconfig_clk

Relógio de trava: src_divided_osc_clk

Modelo de atraso: 2_slow_vid2_100c: -1,474 espera: 0,027

Modelo de atraso: 2_slow_vid2b_100c: -1,574 espera: 0,167

Modelo de atraso: MIN_fast_vid2a_0c: -1.193 espera: 0,216

Modelo de atraso: MIN_fast_vid2a_100c: -1.304 espera: 0,186

Modelo de atraso: MIN_fast_vid2_100c: -1.244 espera: 0,093

Exemplo de falha de sincronização 2

Do nó: eth_f_hw__tiles|z1577a_x0_y0_n0__reset_controller|x_f_tile_soft_reset_ctlr_sip_v1|x_ftile_reset|rst_ctrl|dp_sip_rx_aib_control_select[19]

Nó: eth_f_hw__tiles|z1577a_x0_y0_n0|hdpldadapt_rx_chnl_19~pld_rx_clk1_dcm.reg

Clock de lançamento: src_divided_osc_clk

Clock de trava: IP_INST[0].hw_ip_top|clkdiv2_pll_inst|altera_iopll_0_outclk0

Modelo de atraso: 2_slow_vid2_100c recuperação: -90.597 remoção: 0,244

Modelo de atraso: 2_slow_vid2b_100c recuperação: -90.756 remoção: 0,446

Modelo de atraso: MIN_fast_vid2a_0c recuperação: -90.063 remoção: 0,535

Modelo de atraso: MIN_fast_vid2a_100c recuperação: -90.241 remoção: 0,316

Modelo de atraso: MIN_fast_vid2_100c recuperação: -90.057 remoção: 0,076

Este problema é corrigido a partir do software Intel® Quartus® Prime Pro Edition v22.1.

Para resolver este problema no software Intel® Quartus® Prime Pro Edition versão 21.4 ou anterior, os caminhos de falha relacionados ao controlador soft reset podem ser ignorados com segurança.

No entanto, se você optar por corrigir essas falhas de sincronização incorretas para que elas não sejam relatadas, siga estas etapas:

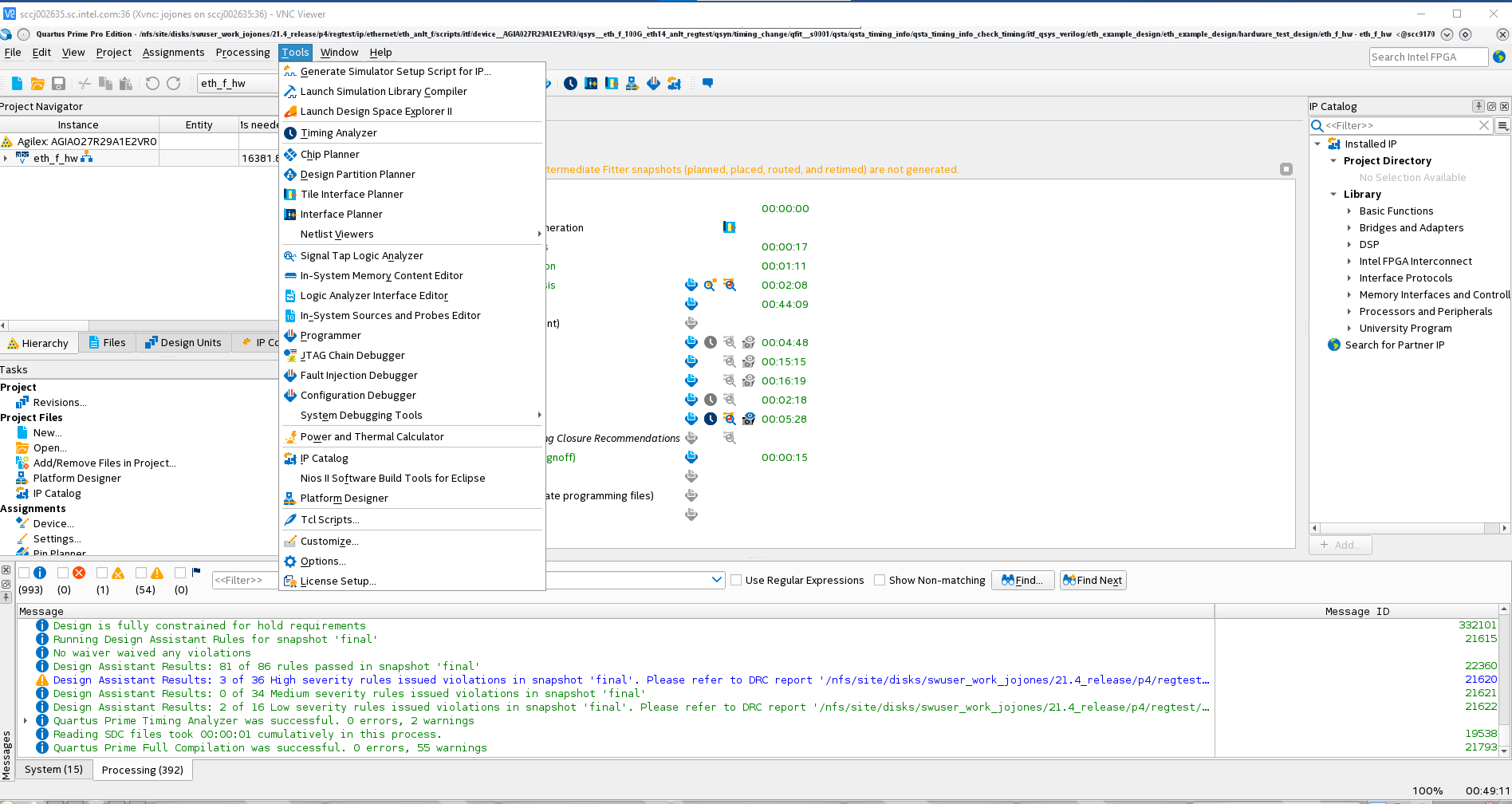

- ) Depois de compilar seu design no software Intel® Quartus® Prime, lance o Analisador de tempo no menu Ferramentas .

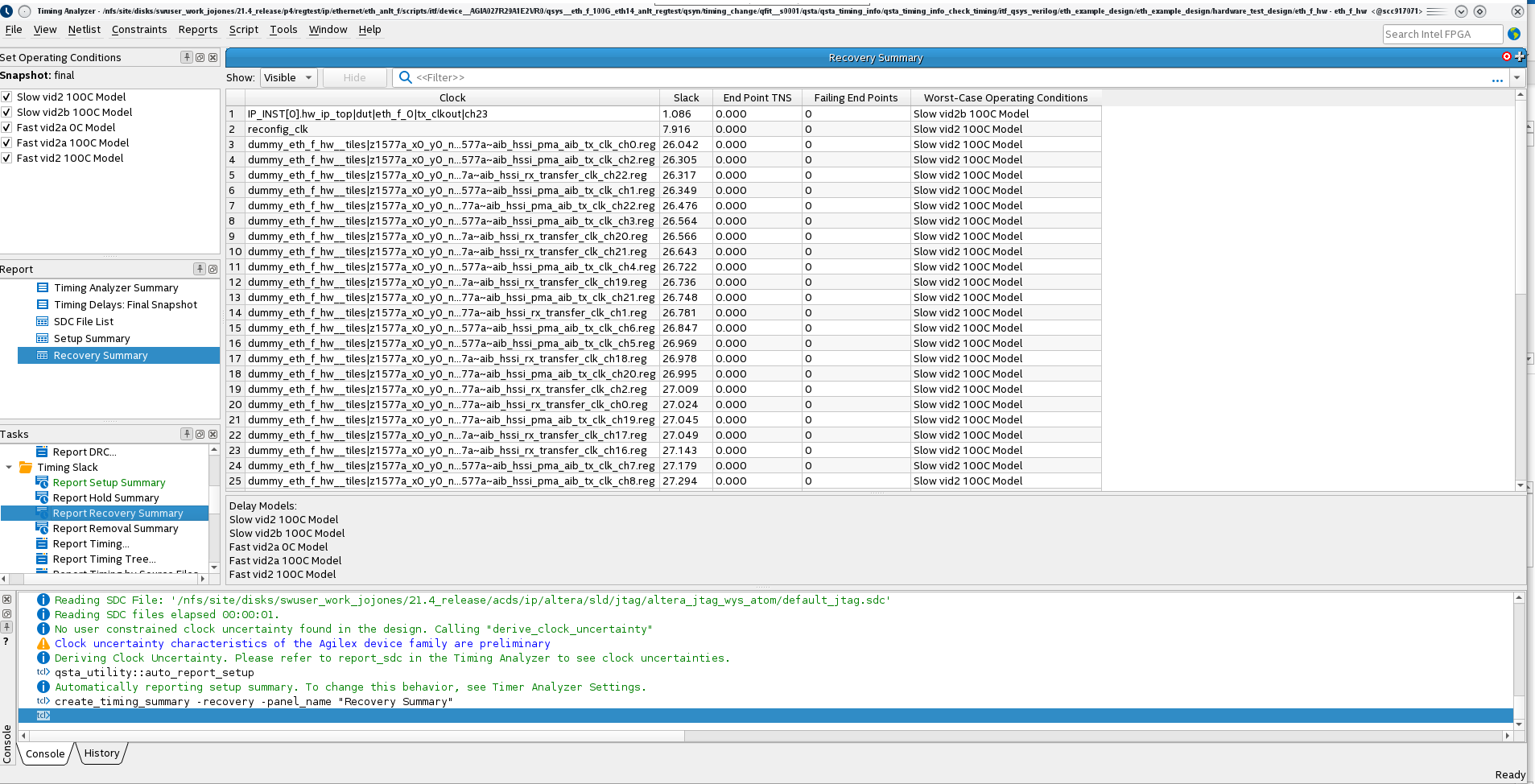

- ) Após o analisador de sincronização ter criado a netlist de sincronização, Gerar vários relatórios de sincronização, incluindo o relatório de tempo de configuração e o relatório de tempo de recuperação.

Neste caso, mesmo que os caminhos falsos não estejam limitados, o analisador de sincronização não relata nenhum erro de sincronização.

-

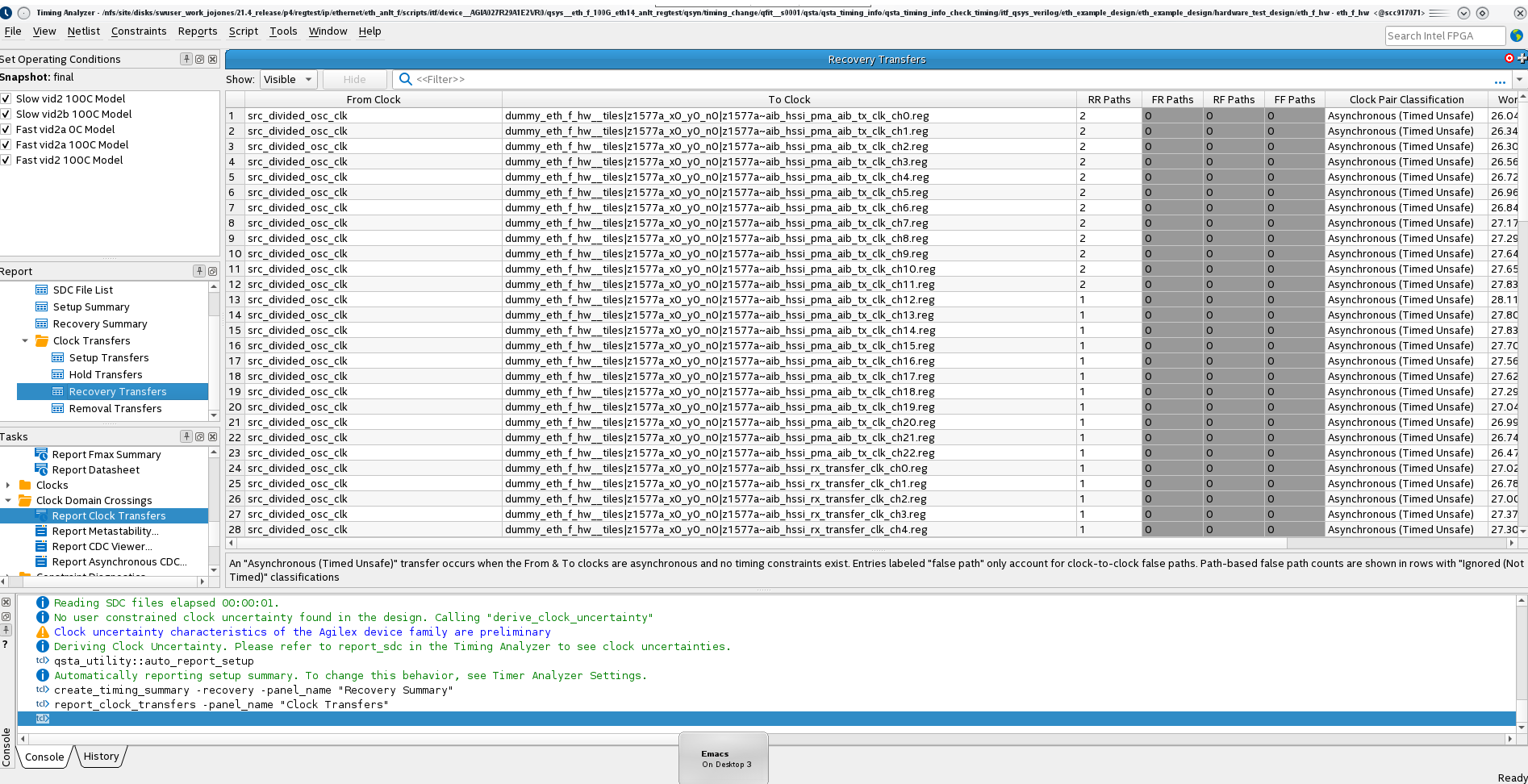

) Veja o relatório de cruzamento do domínio do clock para ver os caminhos de temporização não-limitados.

Isso mostra os caminhos de sincronização desconstreados como Assíncrona (temporizada insegura). Mesmo que o analisador de temporização não reporte um erro de sincronização desses caminhos, eles devem ser limitados para que eles não estejam incluídos na análise de temporização.

Isso mostra os caminhos de sincronização desconstreados como Assíncrona (temporizada insegura). Mesmo que o analisador de temporização não reporte um erro de sincronização desses caminhos, eles devem ser limitados para que eles não estejam incluídos na análise de temporização. -

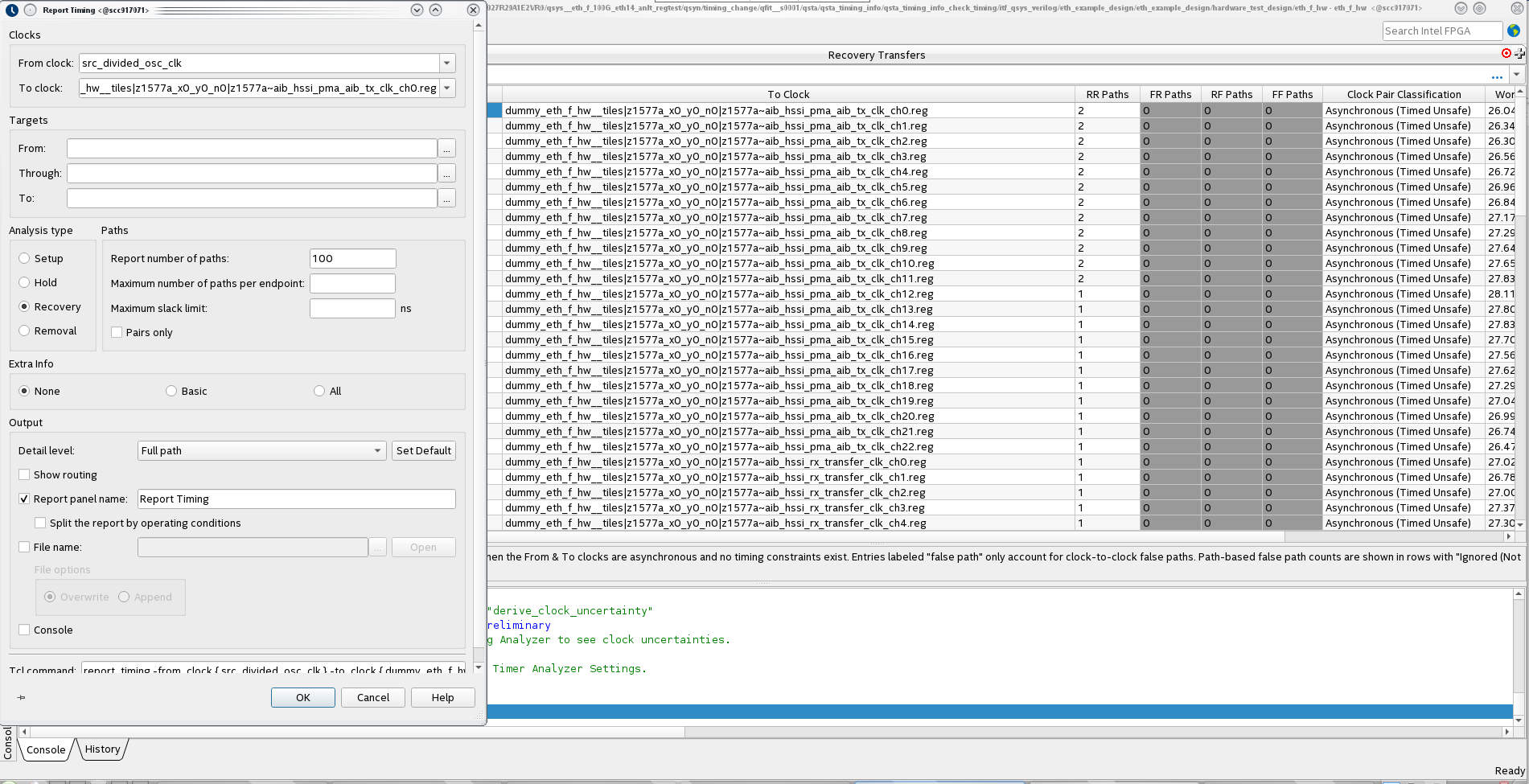

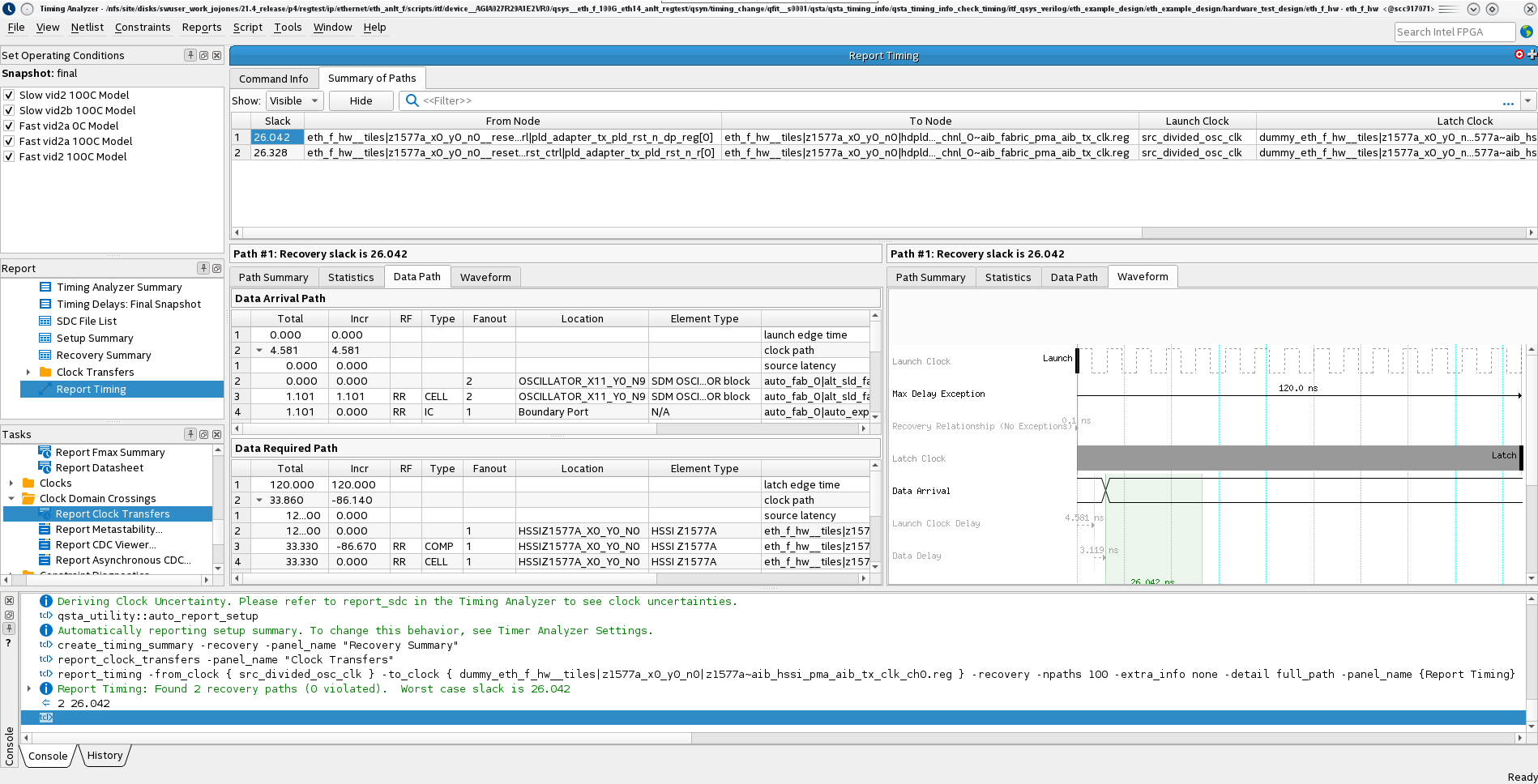

) Para definir uma restrição nesses caminhos, selecione um deles, clique com o botão direito no mouse e selecione Sincronização de Relatório. As opções padrão para o relatório conforme mostrado são suficientes.

-

) Clique em OK. O Relatório de sincronização será gerado.

-

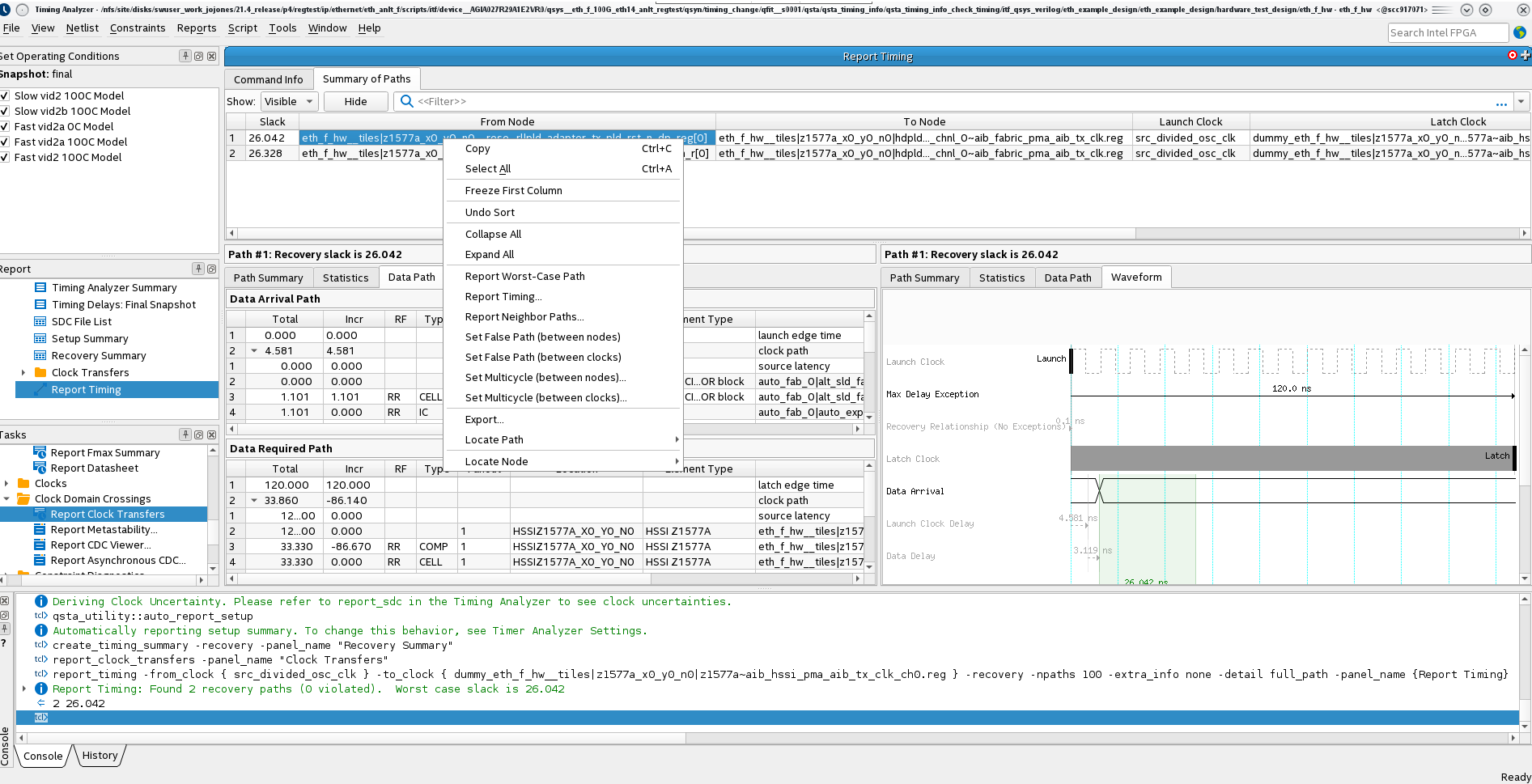

) Para restringir o caminho como um caminho falso, o que significa que ele não será mais incluído na análise de sincronização, clique com o botão direito em qualquer lugar do caminho e selecione Definir caminho falso (entre nós)....

-

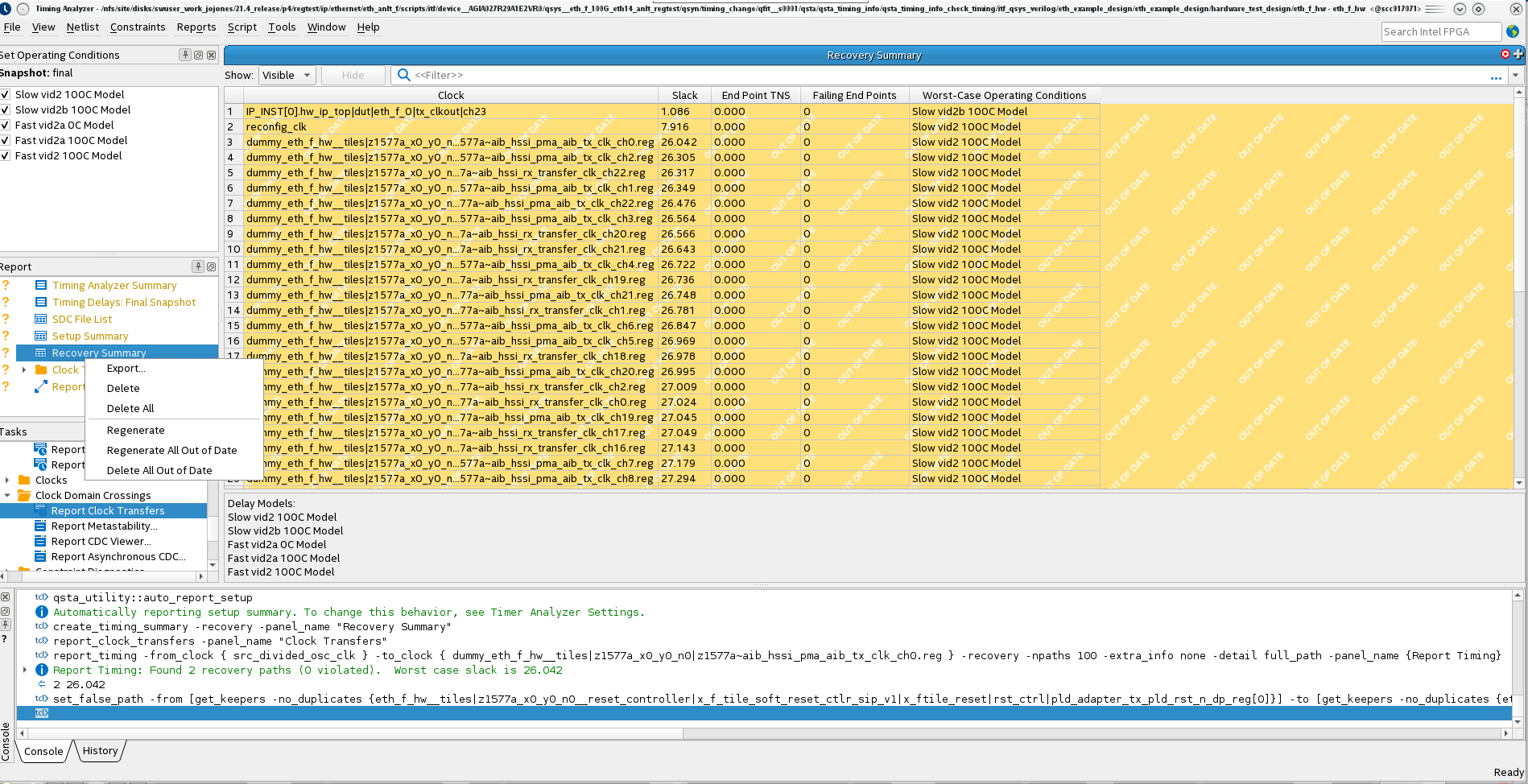

) Para regenerar os relatórios de sincronização, clique com o botão direito em qualquer um dos relatórios mostrados na janela Relatório e selecione Regenerar todos os desatualizes.

Após regenerar os relatórios fora de data, você verá que o caminho de sincronização que você restringiu não aparece mais no relatório de resumo. Isso porque você restringiu o analisador de tempo para não analisar esse caminho falso.

Após regenerar os relatórios fora de data, você verá que o caminho de sincronização que você restringiu não aparece mais no relatório de resumo. Isso porque você restringiu o analisador de tempo para não analisar esse caminho falso. -

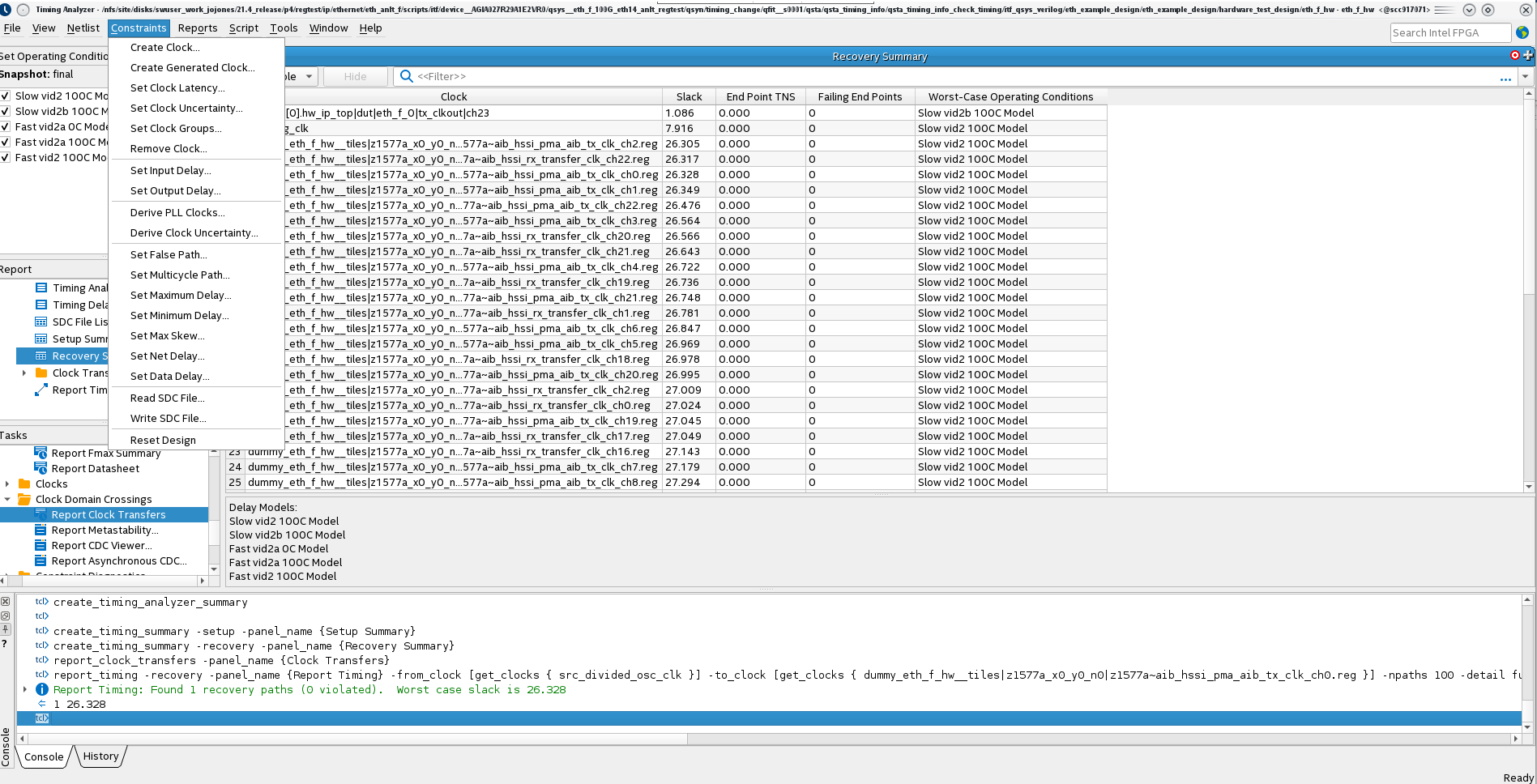

) Repita isso para todos os caminhos que você deseja restringir. Quando terminar, salve todas as alterações que você fez em um novo arquivo .sdc, selecionando Gravar arquivo SDC no menu Restrições .

Você pode selecionar o nome e o local do arquivo .sdc a ser escrito.

O arquivo .sdc gerado incluirá todas as restrições dos arquivos .sdc originalmente lidos para o design, além da nova restrição que você adicionou.

Você pode adicionar este arquivo .sdc ao seu projeto de software Intel Quartus Prime para futuras compilações.

Este problema está programado para ser corrigido em uma versão futura do software Intel Quartus Prime Pro Edition.