Resumo executivo

Resumo executivo

A LLT e outras aplicações sensíveis ao tempo são casos de uso ideais para a aceleração por FPGA. Para atender a esse mercado, a Flyslice Technologies desenvolveu a placa aceleradora FA728Q baseada em FPGA. A plataforma aceleradora FA728Q fornece recursos FPGA potentes, capacidade de armazenamento abundante e interfaces fáceis de usar para os usuários finais. Para acelerar, simplificar e padronizar o desenvolvimento da placa de aceleração, a Flyslice Technologies usou a infraestrutura do OFS, que fornece uma metodologia poderosa para o desenvolvimento rápido de soluções de FPGA usando uma abordagem de “pegar e adaptar”. Usando a infraestrutura do OFS, a Flyslice Technologies integra seu mecanismo de descarga TCP/IP ao FIM base de código aberto, comumente chamado de “shell” do FPGA.

Plano de fundo e desafio

A LLT é a prática moderna de realizar transações de títulos financeiros eletronicamente, com um intervalo mínimo entre a entrada e a execução do pedido. Grandes bancos de investimento, fundos de cobertura e outras instituições financeiras geralmente usam esse método. No passado, as negociações eram realizadas manualmente em vez de por meios eletrônicos, e a realização das transações variava de segundos a minutos. No entanto, com os avanços tecnológicos em hardware e software correspondente, os sistemas podem ser programados para tomar decisões de compra ou venda automaticamente com base em certos sinais e movimentos do mercado, reduzindo os tempos de execução para milissegundos. Com a disponibilidade mais ampla dos produtos de aceleração baseados em FPGA nos últimos anos, os tempos das transações se reduziram ainda mais, agora para microssegundos ou frações de microssegundos.

Ao mesmo tempo, os sistemas de LLT dependem cada vez mais de modelos complexos de algoritmos de negociação exclusivos da estratégia de negociação específica de cada empresa para a interação com o livro de ofertas. As soluções exigem processadores para fins gerais e a computação coprocessada para fins especiais para atender aos requisitos de potência e desempenho das empresas de trading, como na computação heterogênea. Os FPGAs são ideais para implementar algoritmos de negociação personalizados. No entanto, a programação desses dispositivos de aceleração de hardware pode ser demorada e de difícil migração, conforme as famílias de FPGAs melhoram e evoluem.

A Flyslice Technologies, uma empresa com sede na China, está atendendo ativamente à demanda por aceleração heterogênea do data center e computação de alto desempenho, incluindo o segmento de LLT. Ela traz para o mercado plataformas aceleradoras de hardware baseadas em FPGA, funções de propriedade intelectual (IP) de aceleração de FPGA e serviços de design de plataforma baseados em FPGA.

Provedores

Para atender aos requisitos de baixa latência, padronização e portabilidade dos aplicativos de LLT, a Flyslice Technologies desenvolveu sua placa aceleradora FA728Q, que instancia um mecanismo TCP/IP integrado de descarga TCP/IP. Para fazer isso, a Flyslice Technologies modificou o FIM base fornecido na versão de código aberto do OFS. Devido à arquitetura combinável e à abordagem de “pegar e adaptar”, o OFS permitiu que eles simplesmente portassem seu algoritmo para a placa aceleradora FA728Q, aproveitando, ao mesmo tempo, o resto da infraestrutura fornecida, incluindo os drivers de software e as bibliotecas do OFS, fazendo apenas modificações mínimas.

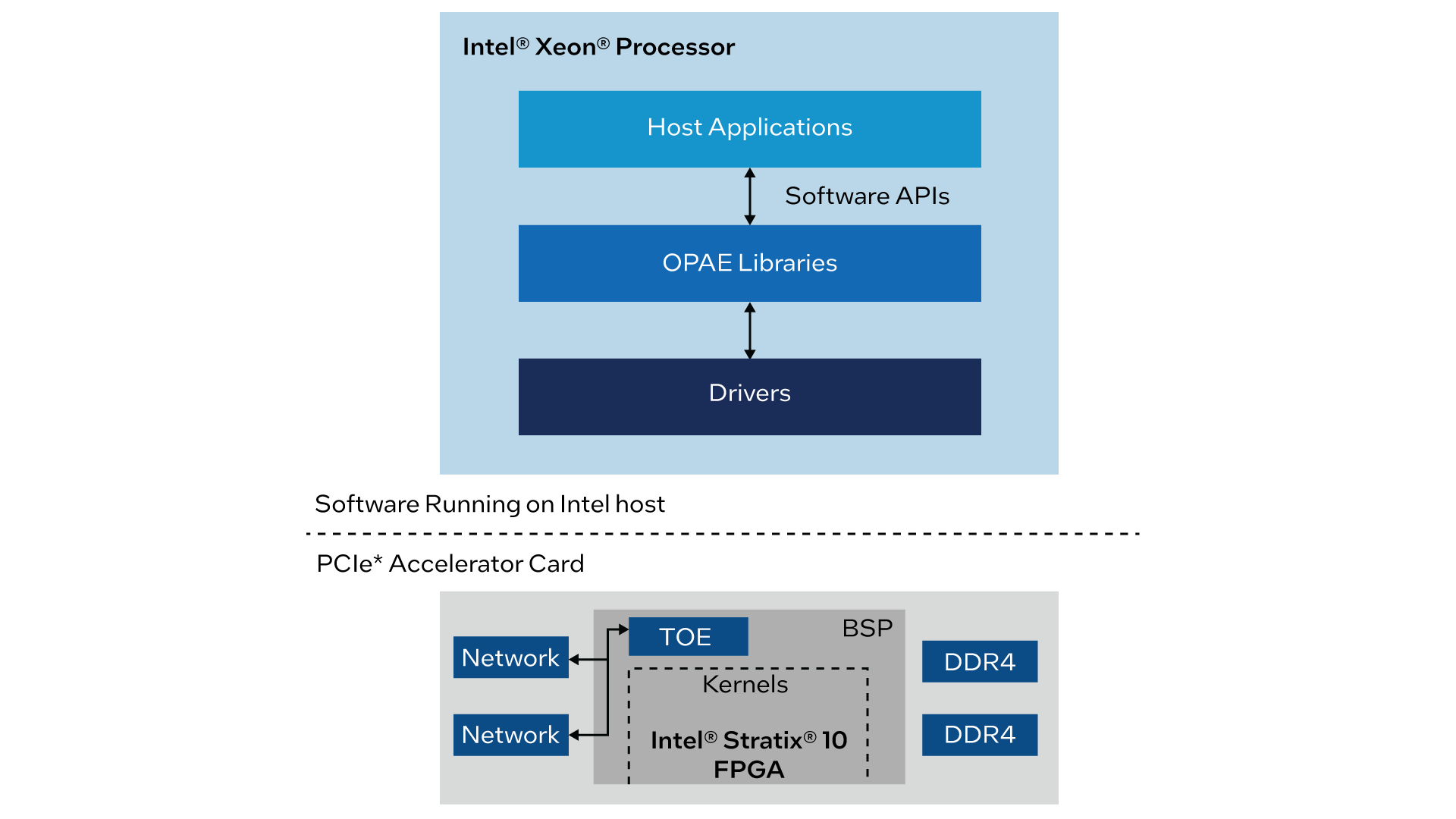

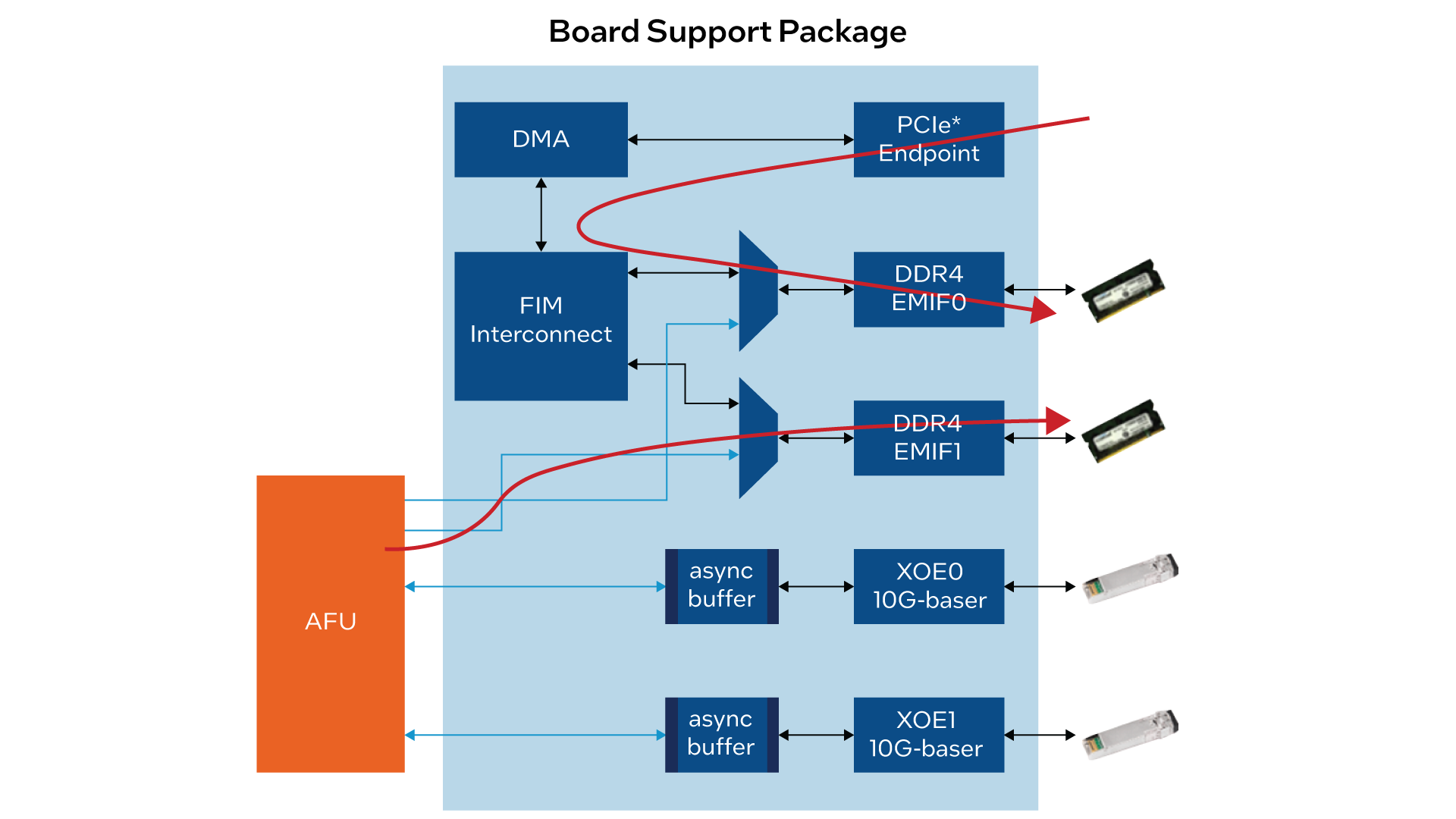

O OFS é uma infraestrutura de hardware e software de código aberto que fornece todos os principais componentes de design, software e infraestrutura necessários para impulsionar o desenvolvimento de placas ou cargas de trabalho personalizadas baseadas em FPGA. A infraestrutura do OFS consiste no FIM, comumente chamado de “shell”, e em uma região de unidade funcional aceleradora (AFU, Accelerator Functional Unit), uma região designada para desenvolvimento de cargas de trabalho. Utilizando o OFS e a placa FGPA — ou o FIM — os desenvolvedores podem aproveitar a infraestrutura de código aberto — ou o FIM base — para desenvolver rapidamente um FIM personalizado para sua placa com base no aplicativo ou setor de destino. O OFS também vem com um pacote de suporte ao acelerador (ASP, Accelerator Support Package) do oneAPI, que pode ser usado para abstrair o fluxo de hardware e design do FPGA. O OFS economiza tempo dos desenvolvedores, aumenta a portabilidade em todas as gerações de FPGA, utiliza interfaces padrão do setor e fornece um fluxo de design opcional de alto nível usando a oneAPI.

A placa aceleradora FA728Q está disponível hoje e é uma placa aceleradora de FPGA baseada em PCIe de ponta que oferece 32 GB de memória DDR4 integrada e três soquetes QSFP28 para suportar até 100 GbE para cada interface. A placa aceleradora FA728Q também é habilitada com a oneAPI por meio da infraestrutura do OFS, para os clientes poderem implementar seus kernels em RTL ou migrar algoritmos da CPU/GPU para linguagens de design de alto nível, incluindo C/C++. O Intel oneAPI Base Toolkit também ajuda a sintetizar e otimizar os kernels para recursos de FPGA, melhorando ainda mais o tempo de lançamento no mercado.

A Flyslice Technologies também começou a desenvolver placas baseadas em FPGA Intel Agilex®, incluindo a placa FA927S que usa o FPGA Intel Agilex 7 série I e a placa FA925E que usa o FPGA Intel Agilex 7 série F.

A placa FA927S apresenta altas taxas do transceptor de até 116 Gbps, PCIe 5.0 x16 e compatibilidade com Compute Express Link (CXL). Ela se destina a aplicativos com uso intenso de largura de banda e está disponível agora para desenvolvimento baseado em RTL. A placa FA927S suportará o OFS no primeiro trimestre de 2024.

Por outro lado, a placa FA925E oferece quatro bancos DDR4 de 8 GB e quatro bancos de 4 GB, totalizando 48 GB de memória integrada. Ela é projetada para aplicativos com requisitos de alta capacidade de memória externa e grande largura de banda. A placa é totalmente compatível com o OFS e estará disponível até o final de 2023. Consulte a Tabela 1 para comparar as três placas aceleradoras.

Tabela 1. Tabela Comparativa

|

|

|

|

|

|---|---|---|---|

| Potência | 215 W | 200 W | 150 W |

| Requisito de resfriamento | Ativo/passivo (opcional) | Ativo/passivo (opcional) | Ativo/passivo (opcional) |

| Fator de forma | PCIe de comprimento 3/4, slot duplo e altura completa | PCIe de meio comprimento, slot duplo e altura completa | PCIe de comprimento 3/4, slot duplo e altura completa |

| Interfaces de rede | Portas QSFP28 triplas: 3x 100 GbE/40 GbE | Portas QSFP28 duplas: 2x 100 GbE/40 GbE | Portas QSFP28 duplas: 2x 100 GbE/40 GbE |

| Interfaces de memória | 4x DDR4 de 8 GB, 2.400 MHz, com ECC | 4x DDR4 de 8 GB, 2.400 MHz, com ECC | 4x DDR4 de 8 GB e 4x DDR4 de 4 GB, 2.400 MHz com ECC |

| Interfaces PCIe | - | 5.0 x16 | - |

| Interfaces de extensão | - | 2 conectores SAS slim de 8 pinos para extensão PCIe 4.0 | - |

| Porta de gerenciamento | Micro-USB | Micro-USB | Micro-USB |

| Dispositivo FPGA | 1SX280HN2F43E2VG | AGIB027R29A1E2VR3 | AGFB027R25A2E2V |

Resultados

A função de IP do mecanismo de descarga implementada pela Flyslice Technologies na placa FA728Q é otimizada para latência e desempenho para atender aos requisitos de LLT. No modo de aceleração, a latência de transmissão do TCP é inferior a 100 ns, garantindo conexões estáveis e de baixa latência para aplicações de rede críticas quanto ao tempo. A Tabela 2 mostra a latência medida para várias conexões. A Tabela 3 mostra as interfaces PCIe 3.0 x16 e DDR de alta largura de banda.

| Especificação | Econômico |

|---|---|

| Máximo de conexões TCP/UDP | 63 para TCP, 63 para UDP |

| Latência do TX do TCP (modo de aceleração) | 15 ciclos de clock |

| Latência do TX do TCP (modo de não aceleração) | 46 ciclos de clock |

| Latência do RX do TCP | 32 ciclos de clock |

| Latência do TX do UDP | 42 ciclos de clock para um pacote de 512 bytes, 18 ciclos de clock para um pacote de 128 bytes |

| Latência do RX do UDP | 23 ciclos de clock |

| Latência de loopback para kernels da oneAPI | 18 ciclos de clock |

Tabela 2. Especificação do mecanismo de descarga de TCP/IP (TOE)

Nota:

1. Um ciclo de clock corresponde a 6,4 ns

2. A latência do TX é contada da borda do EOP de pacotes para dados válidos no XGMII TXC

3. A latência do RX é contada do SOP de pacotes para dados válidos no XGMII RXC

| Caminho dos dados | Larguras de banda |

|---|---|

| Memória de gravação do host | 8.287,68 MBps para bloco de 8.192 KB |

| Memória de leitura do host | 8.241,19 MBps para bloco de 8.192 KB |

| Memória de gravação do kernel | 16.909,6 MBps para bloco de 4.096 MB |

| Memória de leitura do kernel | 17.340,3 MBps para bloco de 4.096 MB |

Tabela 3. Largura de banda fornecida por interface individual

O OFS nos ajudou a criar uma plataforma aceleradora necessária com mais facilidade e rapidez para os clientes, desde drivers de APIs de software até o hardware subjacente, como um conjunto completo de equipamentos.

Como começar a acelerar o FPGA usando OFS

Os desenvolvedores de FPGA podem aproveitar a placa aceleradora FA728Q e a placa habilitada para OFS, usando a documentação de código aberto e o código-fonte para começar a criar sua carga de trabalho personalizada.

A tabela a seguir descreve como um desenvolvedor pode iniciar o desenvolvimento de cargas de trabalho baseadas em FPGA usando a placa de aceleração da Flyslice Technologies.

| Aproveite a aceleração de FPGA para sua carga de trabalho | |

|---|---|

| Etapa 1: escolha uma placa | Veja a placa habilitada para OFS da Flyslice Technologies, a placa aceleradora FA728Q |

| Etapa 2: avalie os recursos de código aberto de OFS |

A Flyslice Technologies fornecerá a versão correspondente da documentação técnica do OFS. |

| Etapa 3: acesse o código de hardware e software de código aberto |

A Flyslice Technologies fornecerá o código de software e hardware correspondente do OFS. Essa é sua distribuição específica do código base do OFS fornecido pela Intel. |

| Etapa 4: desenvolva carga de trabalho usando RTL ou C/C++ (usando oneAPI) |

Siga o fluxo de RTL de OFS OU O OFS habilita a compilação de kernels oneAPI. Utilize o fluxo de desenvolvimento oneAPI e crie cargas de trabalho de FPGA em C/C++. |