Problema crítico

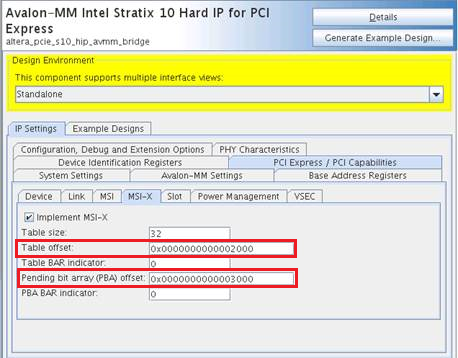

Devido a um problema no software Intel® Quartus® Prime Pro Edition versão 19.2 ou anterior, os parâmetros MSI-X abaixo mostrados na GUI não combinam com os params no RTL gerado.

- Deslocamento da tabela

- Deslocamento pendente de matriz de bits (PBA)

Para resolver este problema, modifique os parâmetros abaixo no "altera_pcie_s10_hip_avmm_bridge.v".

parâmetro [28:0] pf0_pci_msix_pba_offset = 29'h2000,

parâmetro [28:0] pf0_pci_msix_table_offset = 29'h3000

Este problema é corrigido no software Intel® Quartus® Prime Pro versão 19.3 e além.